# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

VLSI DESIGN (J414A)

[R20]

B.TECH ECE

(IV YEAR – I SEM)

(2022-23)

# J. B. INSTITUTE OF ENGINEERING AND TECHNOLOGY (UGC AUTONOMOUS)

Accredited by NBA & NAAC,

Approved by AICTE & Permanently affiliated to JNTUH

Bhaskar Nagar, Yenkapally(V), Moinabad(M), Ranaga Reddy(D),Hyderabad – 500 075,

Telanagana, India.

| AY 2020-21               | J. B. Institute of Engineering and Technology | B. Tech         |   |     |

|--------------------------|-----------------------------------------------|-----------------|---|-----|

| Onwards                  | (UGC Autonomous)                              | IV Year – I Sem |   |     |

| Course<br>Code:<br>J414A | VLSI DESIGN                                   | L               | Т | P/D |

| Credits: 3               |                                               | 3               | 0 | 0   |

Pre-Requisites:Nill

## **Course Objectives:**

The Student will

- 1. visualize MOS fabrication technologies and understand electrical properties of MOS, CMOS and Bi CMOS circuits.

- 2. Draw integrated circuit layouts following design rules.

- 3. Learn combinational circuit, do verification, power optimization and network testing.

- 4. Use power optimization techniques.

- 5. Design validation procedures and testing of sequential circuits.

#### Module 1:

#### **Unit 1 Introduction:**

Introduction to IC Technology-MOS, PMOS, NMOS, CMOS and Bi-CMOS

**Unit 2 Basic Electric Properties:** Basic electrical Properties of MOS and Bi-CMOS Circuits: Ids-Vds relationships. MOS transistor threshold voltage, gm, gds, Figure of merit, pass transistor, NMOS Inverter, Various pull ups, CMOS Inverter analysis and design, BiCMOS inverters.

#### **Module 2:**

#### **Unit-I- VLSI Circuit Design Processes:**

VLSI Design Flow, MOS Layers, Stick Diagrams, Design Rules and layout, 2 µm CMOS design rules for wires.

#### Unit 2:

Contacts and Transistors layout Diagrams for NMOS and CMOS Inverters and Gates, Scaling of MOS Circuits.

#### Module 3:

#### **Unit-I - Gate Level Design**

Language features of Python, Data types, data structures, Control of flow, functions, modules, packaging, file handling, data/time operations, classes, Exception handling.

#### Module-4

#### **Unit-I- Data path Subsystems**

Subsystems Design, Shifters, Adders, ALUs, Multipliers, Parity generators, comparators, Zero/One Detectors, Counters

Unit-II Array Subsystems: SRAM, DRAM, ROM, Serial Access Memories

#### Module-5

#### **Unit-I- Programmable Logic Devices**

PLAs, FPGAs, CPLDs, Standard Cells, Programmable Array Logic, design Approach, Parameters influencing low power design.

**Unit-II- CMOS Testing:** CMOS Testing, Need for testing, Test Principles, Design Strategies for test chip level Test Techniques.

#### **TEXT BOOKS:**

- 1. Essentials of VLSI circuits and systems-Kamran Eshraghian, Eshraghian Dougles and A.Pucknell, PHI, 2005 Edition.

- 2. CMOS VLSI Design-A Circuits and systems perspective, Neil H.E. Weste, David Harris, Ayan Banerjee, 3rd Ed, Pearson, 2009w

# **UNIT-I**

# IC Technologies

- Introduction

- MOS

- PMOS

- NMOS

- CMOS

&

• BiCMOS

**Technologies**

## **Basic Electrical Properties of MOS and BiCMOS Circuits**

- I<sub>DS</sub> V<sub>DS</sub> relationships

- MOS transistor Threshold

Voltage V<sub>T</sub> figure of merit-ω0

- Transconductance-g<sub>m</sub>, g<sub>ds</sub>;

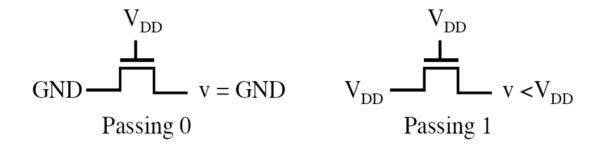

- Pass transistor

- NMOS Inverter, Various pull ups, CMOS Inverter analysis and design

- Bi-CMOS Inverters

#### **INTRODUCTION TO IC TECHNOLOGY**

The development of electronics endless with invention of vaccum tubes and associated electronic circuits. This activity termed as vaccum tube electronics, afterward the evolution of solid state devices and consequent development of integrated circuits are responsible for the present status of communication, computing and instrumentation.

- The first vaccum tube diode was invented by **john ambrase Fleming** in 1904.

- The vaccum triode was invented by **lee de forest** in 1906.

Early developments of the Integrated Circuit (IC) go back to 1949. German engineer Werner Jacobi filed a patent for an IC like semiconductor amplifying device showing five transistors on a common substrate in a 2-stage amplifier arrangement. Jacobi disclosed small cheap of hearing aids.

Integrated circuits were made possible by experimental discoveries which showed that semiconductor devices could perform the functions of vacuum tubes and by mid-20th-century technology advancements in semiconductor device fabrication.

The integration of large numbers of tiny transistors into a small chip was an enormous improvement over the manual assembly of circuits using electronic components.

The integrated circuits mass production capability, reliability, and building-block approach to circuit design ensured the rapid adoption of standardized ICs in place of designs using discrete transistors.

An integrated circuit (IC) is a small semiconductor-based electronic device consisting of fabricated transistors, resistors and capacitors. Integrated circuits are the building blocks of most electronic devices and equipment. An integrated circuit is also known as a chip or microchip.

There are two main advantages of ICs over discrete circuits: cost and performance. Cost is low because the chips, with all their components, are printed as a unit by photolithography rather than being constructed one transistor at a time. Furthermore, much less material is used to construct a packaged IC die than a discrete circuit. Performance is high since the components switch quickly and consume little power (compared to their discrete counterparts) because the components are small and positioned close together. As of 2006, chip areas range from a few square millimeters to around 350 mm<sup>2</sup>, with up to 1 million transistors per mm

## **IC Invention:**

| Inventor                                            | Year         | Circuit                                                             | Remark                                                                      |

|-----------------------------------------------------|--------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Fleming                                             | 1904<br>1906 | Vacuum tube diode<br>Vacuum triode                                  | large expensive, power-<br>hungry, unreliable                               |

| William Shockley<br>(Bell labs)                     | 1945         | Semiconductor replacing vacuum tube                                 |                                                                             |

| Bardeen and<br>Brattain and<br>Shockley (Bell labs) | 1947         | Point Contact transfer resistance device "BJT"                      | Driving factor of growth of the VLSI technology                             |

| Werner Jacobi<br>(Siemens AG)                       | 1949         | 1 <sup>st</sup> IC containing amplifying<br>Device 2stage amplifier | No commercial use reported                                                  |

| Shockley                                            | 1951         | Junction Transistor                                                 | "Practical form of transistor"                                              |

| Jack Kilby (Texas Instruments)                      | July 1958    | Integrated Circuits F/F With 2-T Germanium slice and gold wires     | Father of IC design                                                         |

| Noyce Fairchild<br>Semiconductor                    | Dec. 1958    | Integrated Circuits Silicon                                         | "The Mayor of Silicon<br>Valley"                                            |

| Kahng Bell Lab                                      | 1960         | First MOSFET                                                        | Start of new era for semiconductor industry                                 |

| Fairchild<br>Semiconductor<br>And Texas             | 1061         | First Commercial  IC                                                |                                                                             |

| Frank Wanlass  (Fairchild Semiconductor)            | 1963         | CMOS                                                                |                                                                             |

| Federico Faggin  (Fairchild Semiconductor)          | 1968         | Silicon gate IC technology                                          | Later Joined Intel to lead<br>first CPU Intel 4004 in 1970<br>2300 T on 9mm |

| Zarlink<br>Semiconductors                           | Recently     | M2A capsule for endoscopy                                           | take photographs of digestive tract 2/sec.                                  |

#### Moore's Law:

- Gordon E. Moore Chairman Emeritus of Intel Corporation

- 1965 observed trends in industry of transistors on ICs vs release dates

- Noticed number of transistors doubling with release of each new IC generation

- Release dates (separate generations) were all 18-24 months apart

"The number of transistors on an integrated circuit wills double every 18

The level of integration of silicon technology as measured in terms of number of devices per IC Semiconductor industry has followed this prediction with surprising accuracy.

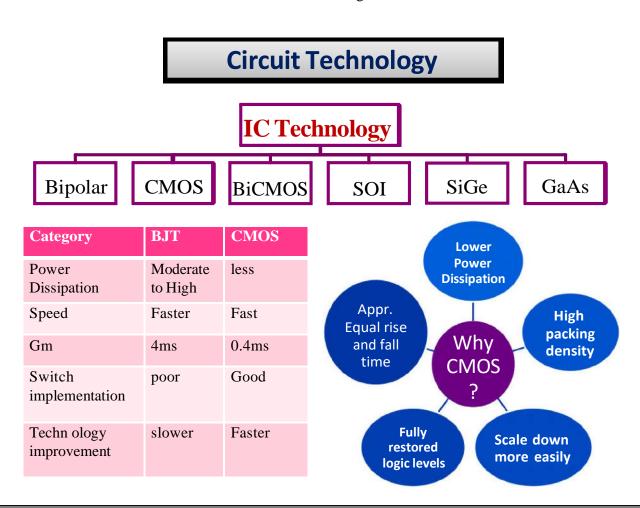

#### **IC Technology:**

- Speed / Power performance of available technologies

- The microelectronics evolution

- SIA Roadmap

- Semiconductor Manufacturers 2001 Ranking

#### **Scale of Integration:**

#### • Small scale integration(SSI) --1960

The technology was developed by integrating the number of transistors of 1-100 on a single chip. Ex: Gates, flip-flops, op-amps.

#### Medium scale integration(MSI) --1967

The technology was developed by integrating the number of transistors of 100-1000 on a single chip. Ex: Counters, MUX, adders, 4-bit microprocessors.

#### • Large scale integration(LSI) --1972

The technology was developed by integrating the number of transistors of 1000-10000 on a single chip. Ex:8-bit microprocessors,ROM,RAM.

#### • Very large scale integration(VLSI) -1978

The technology was developed by integrating the number of transistors of 10000-1Million on a single chip. Ex:16-32 bit microprocessors, peripherals, complimentary high MOS.

#### • Ultra large scale integration(ULSI)

The technology was developed by integrating the number of transistors of 1Million-10 Millions on a single chip. Ex: special purpose processors.

#### • Giant scale integration(GSI)

The technology was developed by integrating the number of transistors of above 10 Millions on a single chip. Ex: Embedded system, system on chip.

- ✓ Fabrication technology has advanced to the point that we can put a complete system on a single chip.

- ✓ Single chip computer can include a CPU, bus, I/O devices and memory.

- ✓ This reduces the manufacturing cost than the equivalent board level system with higher performance and lower power.

#### **MOS TECHNOLOGY:**

MOS technology is considered as one of the very important and promising technologies in the VLSI design process. The circuit designs are realized based on pMOS, nMOS, CMOS and BiCMOS devices.

The pMOS devices are based on the p-channel MOS transistors. Specifically, the pMOS channel is part of a n-type substrate lying between two heavily doped p+ wells beneath the source and drain electrodes. Generally speaking, a pMOS transistor is only constructed in consort with an NMOS transistor.

The nMOS technology and design processes provide an excellent background for other technologies. In particular, some familiarity with nMOS allows a relatively easy transition to CMOS technology and design.

The techniques employed in nMOS technology for logic design are similar to GaAs technology.. Therefore, understanding the basics of nMOS design will help in the layout of GaAs circuits

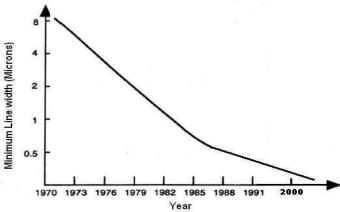

In addition to VLSI technology, the VLSI design processes also provides a new degree of freedom for designers which helps for the significant developments. With the rapid advances in technology the size of the ICs is shrinking and the integration density is increasing.

The minimum line width of commercial products over the years is shown in the graph below.

The graph shows a significant decrease in the size of the chip in recent years which implicitly indicates the advancements in the VLSI technology.

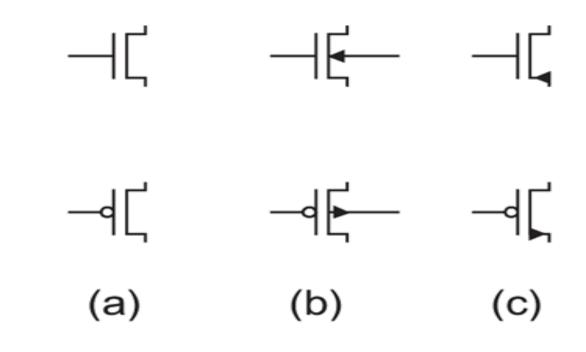

#### **MOS Transistor Symbol:**

# FIG 2.1 MOS transistor symbols

### ENHANCEMENT AND DEPLETION MODE MOS TRANSISTORS

MOS Transistors are built on a silicon substrate. Silicon which is a group IV material is the eighth most common element in the universe by mass, but very rarely occurs as the pure free element in nature. It is most widely distributed in dusts, sands, planetoids, and planets as various forms of silicon dioxide (silica) or silicates. It forms crystal lattice with bonds to four neighbours. Silicon is a semiconductor. Pure silicon has no free carriers and conducts poorly. But adding dopants to silicon increases its conductivity. If a group V material i.e. an extra electron is added, it forms an n-type semiconductor. If a group III material i.e. missing electron pattern is formed (hole), the resulting semiconductor is called a p-type semiconductor.

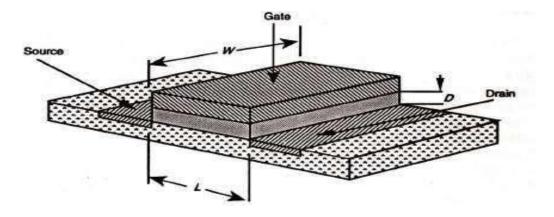

A junction between p-type and n-type semiconductor forms a conduction path. Source and Drain of the Metal Oxide Semiconductor (MOS) Transistor is formed by the "doped" regions on the

surface of chip. Oxide layer is formed by means of deposition of the silicon dioxide (SiO<sub>2</sub>) layer which forms as an insulator and is a very thin pattern. Gate of the MOS transistor is the thin layer of "polysilicon (poly)"; used to apply electric field to the surface of silicon between Drain and Source, to form a "channel" of electrons or holes. Control by the Gate voltage is achieved by modulating the conductivity of the semiconductor region just below the gate. This region is known as the channel.

The Metal–Oxide–Semiconductor Field Effect Transistor (MOSFET) is a transistor which is a voltage-controlled current device, in which current at two electrodes, drain and source is controlled by the action of an electric field at another electrode gate having in-between semiconductor and a very thin metal oxide layer. It is used for amplifying or switching electronic signals.

The Enhancement and Depletion mode MOS transistors are further classified as N-type named NMOS (or N-channel MOS) and P-type named PMOS (or P-channel MOS) devices. Figure 1.5 shows the MOSFETs along with their enhancement and depletion modes.

Figure 1.5: (c) Enhancement P-type MOSFET (d) Depletion P-type MOSFET

The depletion mode devices are doped so that a channel exists even with zero voltage from gate to source during manufacturing of the device. Hence the channel always appears in the device. To control the channel, a negative voltage is applied to the gate (for an N-channel device), depleting the

channel, which reduces the current flow through the device. In essence, the depletion-mode device is equivalent to a closed (ON) switch, while the enhancement-mode device does not have the built in channel and is equivalent to an open (OFF) switch. Due to the difficulty of turning off the depletion mode devices, they are rarely used

#### Working of Enhancement Mode Transistor

The enhancement mode devices do not have the in-built channel. By applying the required potentials, the channel can be formed. Also for the MOS devices, there is a threshold voltage  $(V_t)$ , below which not enough charges will be attracted for the channel to be formed. This threshold voltage for a MOS transistor is a function of doping levels and thickness of the oxide layer.

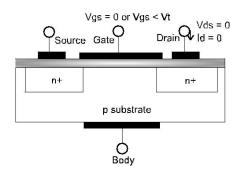

#### Case 1: $V_{gs} = 0V$ and $V_{gs} < V_t$

The device is non-conducting, when no gate voltage is applied ( $V_{gs} = 0V$ ) or ( $V_{gs} < V_t$ ) and also drain to source potential  $V_{ds} = 0$ . With an insufficient voltage on the gate to establish the channel region as N-type, there will be no conduction between the source and drain. Since there is no conducting channel, there is no current drawn, i.e.  $I_{ds} = 0$ , and the device is said to be in the **cut-off region**. This is shown in the Figure 1.7 (a).

Figure 1.7: (a) Cut-off Region

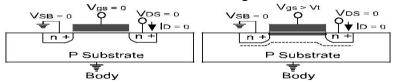

#### Case 2: Vgs > Vt

When a minixmum voltage greater than the threshold voltage  $V_t$  (i.e.  $V_{gs} > V_t$ ) is applied, a high concentration of negative charge carriers forms an inversion layer located by a thin layer next to the interface between the semiconductor and the oxide insulator. This forms a channel between the source and drain of the transistor. This is shown in the Figure 1.7 (b).

**Figure 1.7:** (b) Formation of a Channel

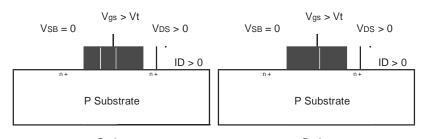

A positive  $V_{ds}$  reverse biases the drain substrate junction, hence the depletion region around the drain widens, and since the drain is adjacent to the gate edge, the depletion region widens in the channel. This is shown in Figure 1.7 (c). This results in flow of electron from source to drain resulting in current Ids. The device is said to operate in **linear region** during this phase. Further increase in  $V_{ds}$ , increases the reverse bias on the drain substrate junction in contact with the inversion layer which causes inversion layer density to decrease. This is shown in Figure 1.7 (d). The point at which the inversion layer density becomes very small (nearly zero) at the drain end is termed pinchoff. The value of  $V_{ds}$  at pinch-off is denoted as  $V_{ds,sat}$ . This is termed as **saturation region** for the MOS device. Diffusion current completes the path from source to drain in this case, causing the channel to exhibit a high resistance and behaves as a constant current source.

Figure 1.7: (c) Linear Region. (d) Saturation Region

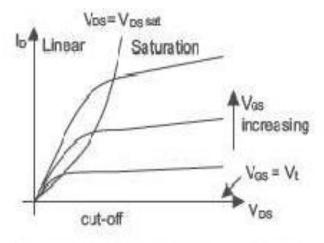

The MOSFET  $I_D$  versus  $V_{DS}$  characteristics (V-I Characteristics) is shown in the Figure 1.8. For  $V_{GS}$  <  $V_t$ ,  $I_D = 0$  and device is in cut-off region. As  $V_{DS}$  increases at a fixed  $V_{GS}$ ,  $I_D$  increases in the linear region due to the increased lateral field, but at a decreasing rate since the inversion layer density is decreasing. Once pinch-off is reached, further increase in  $V_{DS}$  results in increase in  $I_D$ ; due to the formation of the high field region which is very small. The device starts in linear region, and moves into saturation region at higher  $V_{DS}$ .

Figure 1.8: MOS V-I Characteristics

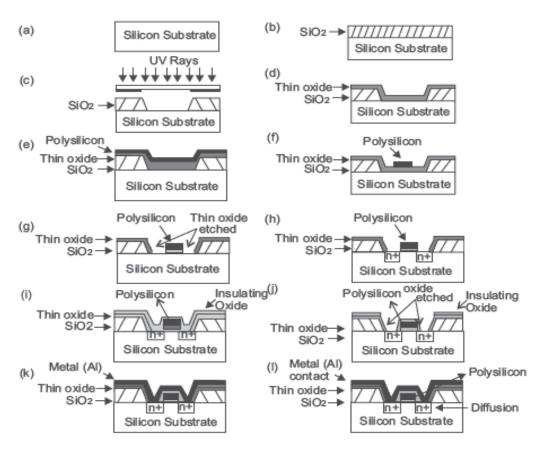

#### **NMOS FABRICATION**

The following description explains the basic steps used in the process of fabrication.

- (a) The fabrication process starts with the oxidation of the silicon substrate.

- It is shown in the Figure 1.9 (a).

- (b) A relatively thick silicon dioxide layer, also called field oxide, is created on the surface of the substrate. This is shown in the Figure 1.9 (b).

- (c) Then, the field oxide is selectively etched to expose the silicon surface on which the MOS transistor will be created. This is indicated in the Figure 1.9 (c).

- (d) This is followed by covering the surface of substrate with a thin, high-quality oxide layer, which will eventually form the gate oxide of the

MOS transistor as illustrated in Figure 1.9 (d).

- (e) On top of the thin oxide, a layer of polysilicon (polycrystalline silicon) is deposited as is shown in the Figure 1.9 (e). Polysilicon is used both as gate electrode material for MOS transistors and also as an interconnect medium in silicon integrated circuits. Undoped polysilicon has relatively high resistivity. The resistivity of polysilicon can be reduced, however, by doping it with impurity atoms.

- (f) After deposition, the polysilicon layer is patterned and etched to form the interconnects and the MOS transistor gates. This is shown in Figure 1.9 (f).

- (g) The thin gate oxide not covered by polysilicon is also etched along, which exposes the bare silicon surface on which the source and drain junctions are to be formed (Figure 1.9 (g)).

- (h) The entire silicon surface is then doped with high concentration of impurities, either through diffusion or ion implantation (in this case with donor atoms to produce n-type doping). Diffusion is achieved by heating the wafer to a high temperature and passing the gas containing desired impurities over the surface. Figure 1.9 (h) shows that the doping penetrates the exposed areas on the silicon surface, ultimately creating two n-type regions (source and drain junctions) in the p-type substrate. The impurity doping also penetrates the polysilicon on the surface, reducing its resistivity.

- (i) Once the source and drain regions are completed, the entire surface is again covered with an insulating layer of silicon dioxide, as shown in

- Figure 1.9 (i).(j) The insulating oxide layer is then patterned in order to provide contact windows for the drain and source junctions, as illustrated in Figure 1.9 (j).

Figure 1.9: Fabrication Process of NMOS Device

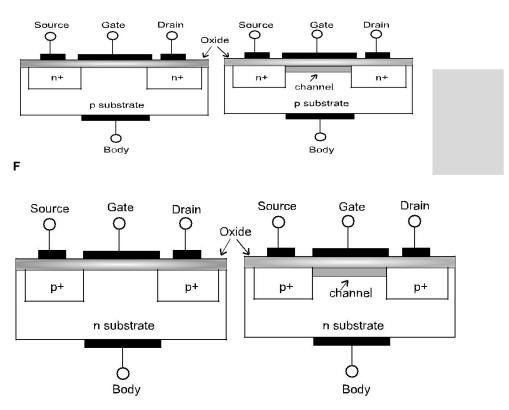

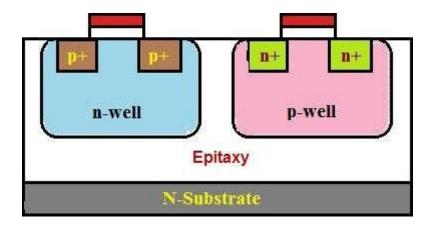

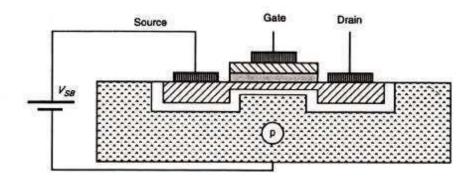

#### **CMOS FABRICATION:**

CMOS fabrication can be accomplished using either of the three technologies:

- N-well technologies/P-well technologies

- Twin well technology

- Silicon On Insulator (SOI)

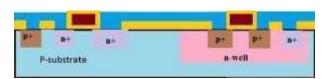

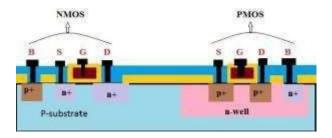

The fabrication of CMOS can be done by following the below shown twenty steps, by which CMOS can be obtained by integrating both the NMOS and PMOS transistors on the same chip substrate. For integrating these NMOS and PMOS devices on the same chip, special regions called as wells or tubs are required in which semiconductor type and substrate type are opposite to each other.

A P-well has to be created on a N-substrate or N-well has to be created on a P-substrate. In this article, the fabrication of CMOS is described using the P-substrate, in which the NMOS transistor is fabricated on a P-type substrate and the PMOS transistor is fabricated in N-well.

The fabrication process involves twenty steps, which are as follows:

#### **N-Well Process**

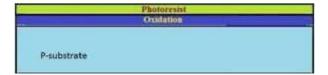

#### **Step1: Substrate**

Primarily, start the process with a P-substrate.

#### **Step2: Oxidation**

The oxidation process is done by using high-purity oxygen and hydrogen, which are exposed in an oxidation furnace approximately at 1000 degree centigrade.

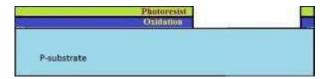

#### **Step3: Photoresist**

A light-sensitive polymer that softens whenever exposed to light is called as Photoresist layer. It is formed.

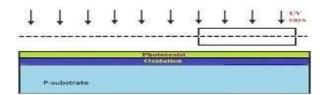

#### **Step4: Masking**

The photoresist is exposed to UV rays through the N-well mask

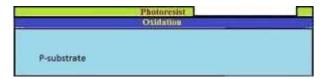

**Step5: Photoresist removal**

A part of the photoresist layer is removed by treating the wafer with the basic or acidic solutio n.

## Step6: Removal of SiO2 using acid etching

The SiO2 oxidation layer is removed through the open area made by the removal of photoresist using hydrofluoric acid.

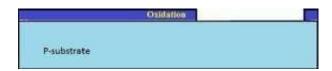

#### **Step7: Removal of photoresist**

The entire photoresist layer is stripped off, as shown in the below figure.

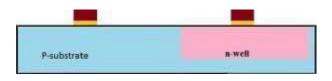

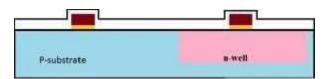

#### **Step8: Formation of the N-well**

By using ion implantation or diffusion process N-well is formed.

#### Step9: Removal of SiO2

Using the hydrofluoric acid, the remaining SiO2 is removed.

#### **Step10: Deposition of polysilicon**

Chemical Vapor Deposition (CVD) process is used to deposit a very thin layer of gate oxide.

Step11: Removing the layer barring a small area for the Gates

Except the two small regions required for forming the Gates of NMOS and PMOS, the remaining layer is stripped off.

#### **Step12: Oxidation process**

Next, an oxidation layer is formed on this layer with two small regions for the formation of the gate terminals of NMOS and PMOS.

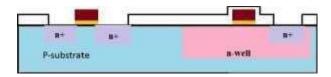

**Step13: Masking and N-diffusion**

By using the masking process small gaps are made for the purpose of N -diffusion.

The n-type (n+) dopants are diffused or ion implanted, and the three n+ are formed for the formation of the terminals of NMOS.

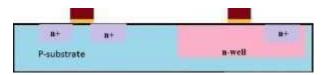

**Step14: Oxide stripping**

The remaining oxidation layer is stripped off.

**Step15: P-diffusion**

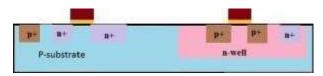

Similar to the above N-diffusion process, the P-diffusion regions are diffused to form the terminals of the PMOS.

Step16: Thick field oxide

A thick-field oxide is formed in all regions except the terminals of the PMOS and NMOS.

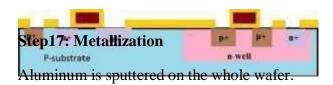

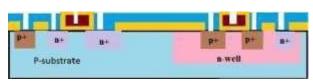

**Step18: Removal of excess metal**

The excess metal is removed from the wafer layer.

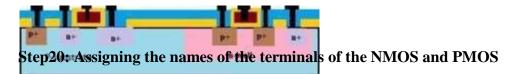

**Step19: Terminals**

The terminals of the PMOS and NMOS are made from respective gaps.

#### **Fabrication of CMOS using P-well process**

Among all the fabrication processes of the CMOS, N-well process is mostly used for the fabrication of the CMOS. P-well process is almost similar to the N-well. But the only difference in p-well process is that it consists of a main N-substrate and, thus, P-wells itself acts as substrate for the N-devices.

#### **Twin tub-CMOS Fabrication Process**

In this process, separate optimization of the n-type and p-type transistors will be provided. The independent optimization of Vt, body effect and gain of the P-devices, N-devices can be made possible with this process.

Different steps of the fabrication of the CMOS using the twintub process are as follows:

- Lightly doped n+ or p+ substrate is taken and, to protect the latch up, epitaxial layer is used.

- The high-purity controlled thickness of the layers of silicon are grown with exact dopant concentrations.

- The dopant and its concentration in Silicon are used to determine electrical properties.

- Formation of the tub

- Thin oxide construction

- Implantation of the source and drain

- Cuts for making contacts

- Metallization

By using the above steps we can fabricate CMOS using twin tub process method.

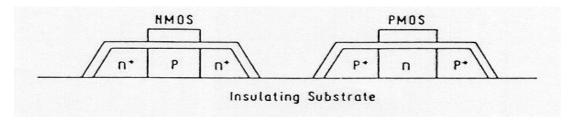

#### Silicon-on-Insulator (SOI) CMOS Process

Rather than using silicon as the substrate material, technologists have sought to use an insulating substrate to improve process characteristics such as speed and latch-up susceptibility. The SOI CMOS technology allows the creation of independent, completely isolated nMOS and pMOS transistors virtually side-by-side on an insulating substrate. The main advantages of this technology are the higher integration density (because of the absence of well regions), complete avoidance of the latch-up problem, and lower parasitic capacitances compared to the conventional p & n-well or twintub CMOS processes. A cross-section of nMOS and pMOS devicesusing SOI processis shown below.

The SOI CMOS process is considerably more costly than the standard p & n-well CMOS process. Yet the improvements of device performance and the absence of latch-up problems can justify its use, especially for deep-sub-micron devices.

#### **Basic Electrical Properties of MOS and Bi CMOS circuits**

#### <u>ID-VDS</u> Characteristics of MOS Transistor:

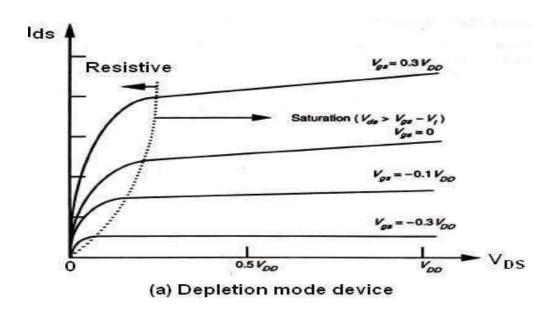

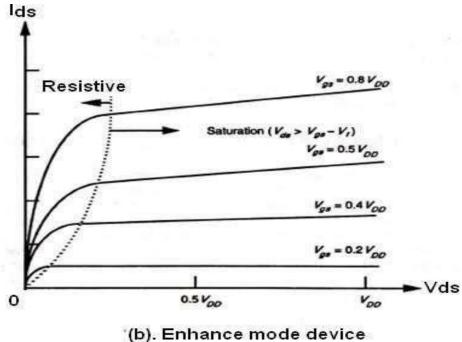

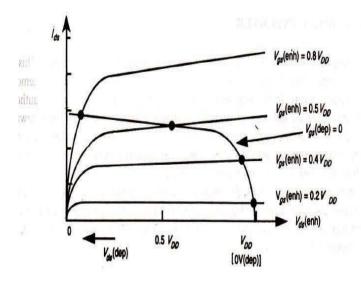

The graph below shows the ID Vs VDS characteristics of an n- MOS transistor for several values of VGS .It is clear that there are two conduction states when the device is ON. The saturated state and the non-saturated state. The saturated curve is the flat portion and defines the saturation region. For Vgs < VDS + Vth, the nMOS device is conducting and ID is independent of VDS. For Vgs > VDS + Vth, the transistor is in the non-saturation region and the curve is a half parabola. When the transistor is OFF (Vgs < Vth), then ID is zero for any VDS value.

The boundary of the saturation/non-saturation bias states is a point seen for each curve in the graph as the intersection of the straight line of the saturated region with the quadratic curve of the non-saturated region. This intersection point occurs at the channel pinch off voltage called VDSAT. The diamond symbol marks the pinch-off voltage VDSAT for each value of VGS. VDSAT is defined as the minimum drain-source voltage that is required to keep the transistor in saturation for a given VGS. In the non-saturated state, the drain current initially increases almost linearly from the origin before bending in a parabolic response. Thus the name ohmic or linear for the non-saturated region.

The drain current in saturation is virtually independent of VDS and the transistor acts as a current

source. This is because there is no carrier inversion at the drain region of the channel. Carriers are pulled into the high electric field of the drain/substrate pn junction and ejected out of the drain terminal.

#### Drain-to-Source Current IDS Versus Voltage VDS Relationships:

The working of a MOS transistor is based on the principle that the use of a voltage on the gate induce a charge in the channel between source and drain, which may then be caused to move from source to drain under the influence of an electric field created by voltage Vds applied between drain and source. Since the charge induced is dependent on the gate to source voltage Vgs then Ids is dependent on both Vgs and Vds.

Let us consider the diagram below in which electrons will flow source to drain .So,the drain current is given by

Charge induced in channel (Qc) Ids =-Isd = Electron transit time( $\tau$ ) Length of the channel Where the transit time is given by  $\tau_{Sd} = ----$ Velocity (v)

#### But velocity $v = \mu Eds$

Where  $\mu$  =electron or hole mobility and  $Eds = Electric \ field \ also \ , \ Eds = Vds/L$   $so,v = \mu.Vds/L \ and \ \tau ds = L^2/\mu.Vds$

The typical values of  $\mu$  at room temperature are given below.

$$\mu_n = 650 \text{ cm}^2/\text{V} \text{ sec (surface)}$$

$\mu_p = 240 \text{ cm}^2/\text{V} \text{ sec (surface)}$

#### **Non-saturated Region:**

Let us consider the Id vs Vd relationships in the non-saturated region. The charge induced in the channel due to due to the voltage difference between the gate and the channel, Vgs (assuming substrate connected to source). The voltage along the channel varies linearly with distance X from the source due to the IR drop in the channel. In the non-saturated state the average value is Vds/2. Also the effective gate voltage Vg = Vgs - Vt where Vt, is the threshold voltage needed to invert the charge under the gate and establish the channel.

Hence the induced charge is  $Q_C = E_g \ \epsilon_{ins} \ \epsilon_O W. L$

Where

Eg = average electric field gate to channel

$\varepsilon$ ins = relative permittivity of insulation between gate and channel  $\varepsilon$ <sub>0</sub>=permittivity

$$E_g = \frac{\left( (V_{gs} - V_t) - \frac{V_{ds}}{2} \right)}{D}$$

Here D is the thickness of the oxide layer. Thus

$$Q_{c} = \frac{WL\varepsilon_{ins}\varepsilon_{0}}{D}\left((V_{gs} - V_{t}) - \frac{V_{ds}}{2}\right)$$

So, by combining the above two equations ,we get

$$I_{ds} = \frac{\varepsilon_{int}\varepsilon_{0}\mu}{D} \frac{W}{L} \left( (V_{gs} - V_{i}) - \frac{V_{ds}}{2} \right) V_{ds}$$

or the above equation can be written as

$$I_{ds} = K \frac{W}{L} \left( (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2} \right)$$

In the non-saturated or resistive region where Vds < Vgs - Vt and

$$K = \frac{\varepsilon_{inx}\varepsilon_0\mu}{D}$$

Generally ,a constant  $\beta$  is defined as

$$\beta = K \frac{W}{L}$$

So that ,the expression for drain -source current will become

$$I_{ds} = \beta \left( (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2} \right)$$

The gate /channel capacitance is

$$C_g = \frac{\varepsilon_{ins}\varepsilon_0WL}{D}$$

(parallel plate)

Hence we can write another alternative form for the drain current as

$$I_{ds} = \frac{C_g \mu}{L^2} \left( (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2} \right)$$

Some time it is also convenient to use gate -capacitance per unit area ,Cg So,the drain current is

$$I_{ds} = C_0 \mu \frac{W}{L} \left( (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2} \right)$$

This is the relation between drain current and drain-source voltage in non-saturated region.

#### **Saturated Region**

Saturation begins when Vds = Vgs - V, since at this point the IR drop in the channel equals the effective gate to channel voltage at the drain and we may assume that the current remains fairly constant as Vds increases further. Thus

$$I_{ds} = K \frac{W}{L} \frac{(V_{gs} - V_t)^2}{2}$$

or we can also write that

$$I_{ds} = \frac{\beta}{2} (V_{gs} - V_i)^2$$

or it can also be written as

$$I_{ds} = \frac{C_g \mu}{2L^2} (V_{gs} - V_t)^2$$

or

$$I_{dr} = C_0 \mu \frac{W}{2L} (V_{gr} - V_t)^2$$

The expressions derived above for Ids hold for both enhancement and depletion mode devices. Here the threshold voltage for the nMOS depletion mode device (denoted as Vtd) is negative.

#### **MOS Transistor Threshold Voltage Vt:**

The gate structure of a MOS transistor consists, of charges stored in the dielectric layers and in the surface to surface interfaces as well as in the substrate itself. Switching an enhancement mode MOS transistor from the off to the on state consists in applying sufficient gate voltage to neutralize these charges and enable the underlying silicon to undergo an inversion due to the electric field from the gate. Switching a depletion mode nMOS transistor from the on to the off state consists in applying enough voltage to the gate to add to the stored charge and invert the 'n' implant region to 'p'.

The threshold voltage Vt may be expressed as:

$$V_t = \phi_{mt} \frac{Q_B - Q_{SS}}{C_0} + 2\phi_{fN}$$

where QD = the charge per unit area in the depletion layer below the oxide Qss = charge density at Si: SiO2 interface

C<sub>0</sub> =Capacitance per unit area.

$\Phi$ ns = work function difference between gate and Si

$\Phi_{fN}$  = Fermi level potential between inverted surface and bulk Si

For polynomial gate and silicon substrate, the value of  $\Phi_{ns}$  is negative but negligible and the magnitude and sign of Vt are thus determined by balancing the other terms in the equation. To evaluate the Vt the other terms are determined as below.

$$Q_B = \sqrt{2 \varepsilon_0 \varepsilon_{Si} q N (2 \phi_{fN} + V_{SB})} \text{ coulomb/m}^2$$

$$\phi_{fN} = \frac{kT}{q} \ln \frac{N}{n_i} \text{ volts}$$

$$Q_{SS} = (1.5 \text{ to } 8) \times 10^{-8} \text{ coulomb/m}^2$$

#### **Body Effect:**

Generally while studying the MOS transistors it is treated as a three terminal device. But, the body of the transistor is also an implicit terminal which helps to understand the characteristics of the transistor. Considering the body of the MOS transistor as a terminal is known as the body effect. The potential difference between the source and the body (Vsb) affects the threshold

voltage of the transistor. In many situations, this Body Effect is relatively insignificant, so we can (unless **otherwise** stated) ignore the Body Effect. But it is not always insignificant, in some cases it can have a tremendous impact on MOSFET circuit performance.

#### **Body effect - nMOS device**

Increasing Vsb causes the channel to be depleted of charge carriers and thus the threshold voltage is raised. Change in Vt is given by  $\Delta Vt = \gamma . (Vsb)^{1/2}$  where  $\gamma$  is a constant which depends on substrate doping so that the more lightly doped the substrate, the smaller will be the body effect The threshold voltage can be written as

$$V_t = V_t(0) + \left(\frac{D}{\varepsilon_{int}\varepsilon_0}\right) \sqrt{2\varepsilon_0\varepsilon_{SI}QN} \cdot (V_{SB})^{1/2}$$

Where Vt(0) is the threshold voltage for Vsd = 0

For n-MOS depletion mode transistors ,the body voltage values at different VDD voltages are given below.

$$VSB = 0 V$$

;  $Vsd = -0.7VDD$  (= - 3.5 V for  $VDD = +5V$ )  $VSB = 5 V$ ;  $Vsd = -0.6VDD$  (= - 3.0 V for  $VDD = +5V$ )

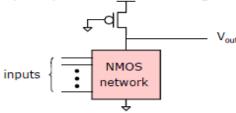

#### nMOS INVERTER:

An inverter circuit is a very important circuit for producing a complete range of logic circuits. This is needed for restoring logic levels, for Nand and Nor gates, and for sequential and memory circuits of various forms .

A simple inverter circuit can be constructed using a transistor with source connected to ground and a load resistor of connected from the drain to the positive supply rail VDD. The output is taken from the drain and the input applied between gate and ground.

But, during the fabrication resistors are not conveniently produced on the silicon substrate and even small values of resistors occupy excessively large areas. Hence some other form of load resistance is used. A more convenient way to solve this problem is to use a depletion mode transistor as the load, as shown in Fig. below.

The salient features of the n-MOS inverter are

- For the depletion mode transistor, the gate is connected to the source so it is always on .

- In this configuration the depletion mode device is called the pull-up (P.U) and the enhancement mode device the pull-down (P.D) transistor.

- With no current drawn from the output, the currents Ids for both transistors must be equal.

#### nMOS Inverter transfer characteristic.

The transfer characteristic is drawn by taking Vds on x-axis and Ids on Y-axis for both enhancement and depletion mode transistors. So,to obtain the inverter transfer characteristic for

Vgs = 0 depletion mode characteristic curve is superimposed on the family of curves for the enhancement mode device and from the graph it can be seen that , maximum voltage across the enhancement mode device corresponds to minimum voltage across the depletion mode transistor.

From the graph it is clear that as Vin(=Vgs p.d. transistor) exceeds the Pulldown threshold voltage current begins to flow. The output voltage Vout thus decreases and the subsequent increases in Vin will cause the Pull down transistor to come out of saturation and become resistive.

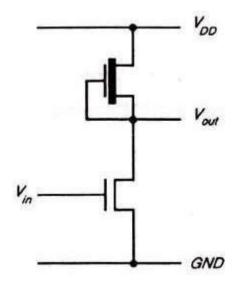

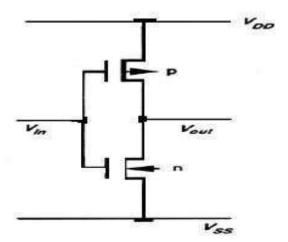

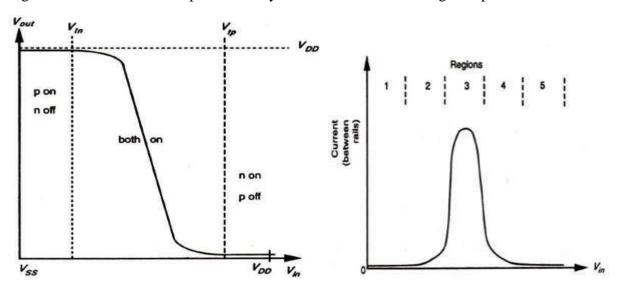

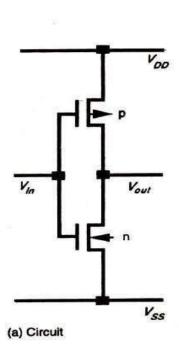

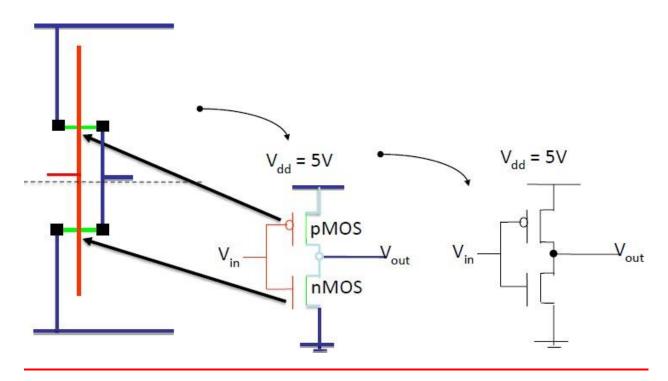

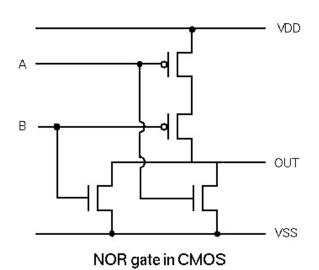

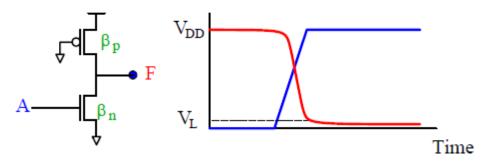

#### **CMOS Inverter:**

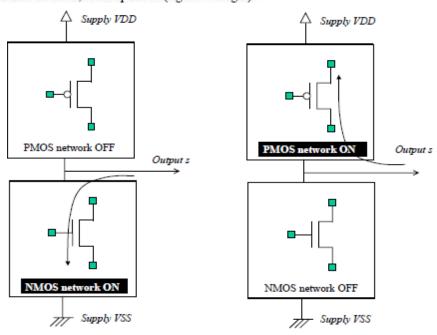

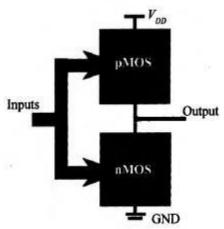

The inverter is the very important part of all digital designs. Once its operation and properties are clearly understood, Complex structures like NAND gates, adders, multipliers, and microprocessors can also be easily done. The electrical behavior of these complex circuits can be almost completely derived by extrapolating the results obtained for inverters. As shown in the diagram below the CMOS transistor is designed using p-MOS and n-MOS transistors.

In the inverter circuit, if the input is high .the lower n-MOS device closes to discharge the capacitive load .Similarly, if the input is low, the top p-MOS device is turned on to charge the capacitive load .At no time both the devices are on ,which prevents the DC current flowing from positive power supply to ground. Qualitatively this circuit acts like the switching circuit, since the p-channel transistor has exactly the opposite characteristics of the n-channel transistor. In the transition region both transistors are saturated and the circuit operates with a large voltage gain. The C-MOS transfer characteristic is shown in the below graph.

Considering the static conditions first, it may be Seen that in region 1 for which Vi,. = logic 0, we have the p-transistor fully turned on while the n-transistor is fully turned off. Thus no current flows through the inverter and the output is directly connected to VDD through the p-transistor.

Hence the output voltage is logic 1 . In region 5 ,  $V_{in} = logic$  1 and the n-transistor is fully on while the p-transistor is fully off. So, no current flows and logic 0 appears at the output.

In region 2 the input voltage has increased to a level which just exceeds the threshold voltage of the n-transistor. The n-transistor conducts and has a large voltage between source and drain; so it is in saturation. The p-transistor is also conducting but with only a small voltage across it, it operates in the unsaturated resistive region. A small current now flows through the inverter from VDD to VSS. If we wish to analyze the behavior in this region, we equate the p-device resistive region current with the n-device saturation current and thus obtain the voltage and current relationships.

Region 4 is similar to region 2 but with the roles of the p- and n-transistors reversed. However, the current magnitudes in regions 2 and 4 are small and most of the energy consumed in switching from one state to the other is due to the larger current which flows in region 3.

Region 3 is the region in which the inverter exhibits gain and in which both transistors are in saturation.

The currents in each device must be the same ,since the transistors are in series. So, we can write that

$$I_{dsp} = -I_{dsn}$$

where

$$I_{dsp} = \frac{\beta_p}{2} (V_{in} - V_{DD} - V_{tp})^2$$

and

$$I_{dsn} = \frac{\beta_n}{2} \left( V_{in} - V_{in} \right)^2$$

Since both transistors are in saturation, they act as current sources so that the equivalent circuit in this region is two current sources in series between VDD and Vss with the output voltage coming from their common point. The region is inherently unstable in consequence and the changeover from one logic level to the other is rapid.

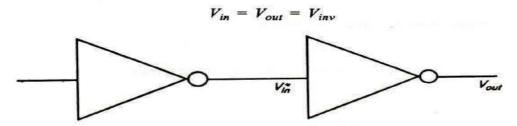

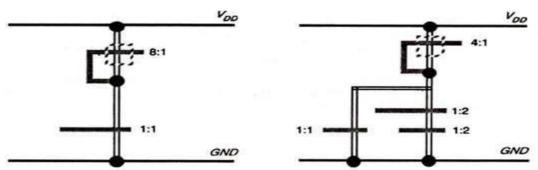

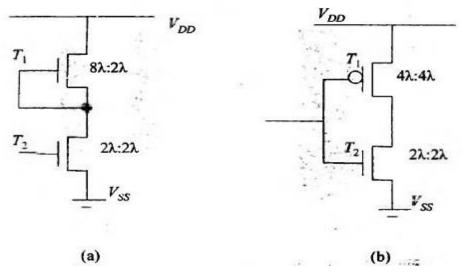

## Determination of Pull-up to Pull –Down Ratio (Zp.u)Zp.d.) for an nMOS Inverter driven by another nMOS Inverter:

Let us consider the arrangement shown in Fig.(a). in which an inverter is driven from the output of another similar inverter. Consider the depletion mode transistor for which Vgs = 0 under all conditions, and also assume that in order to cascade inverters without degradation the condition

Fig.(a).Inverter driven by another inverter.

For equal margins around the inverter threshold, we set  $Vinv = 0.5VDD \cdot At$  this point both transistors are in saturation and we can write that

$$I_{ds} = K \frac{W}{L} \frac{(V_{gs} - V_t)^2}{2}$$

In the depletion mode

$$I_{ds} = K \frac{W_{p.u.}}{L_{p.u.}} \frac{(-V_{td})^2}{2} \text{ since } V_{gs} = 0$$

and in the enhancement mode

$$I_{ds} = K \frac{W_{p.d.}}{L_{p.d.}} \frac{(V_{inv} - V_t)^2}{2}$$

since  $V_{gs} = V_{inv}$

Equating (since currents are the same) we have

$$\frac{W_{p.d.}}{L_{p.d.}} (V_{inv} - V_t)^2 = \frac{W_{p.u.}}{L_{p.u.}} (-V_{td})^2$$

where Wp.d , Lp.d , Wp.u. and Lp.u are the widths and lengths of the pull-down and pull-up transistors respectively.

So, we can write that

$$Z_{p.d.} = \frac{L_{p.d.}}{W_{p.d.}}; Z_{p.u.} = \frac{L_{p.u.}}{W_{p.u.}}$$

we have

$$\frac{1}{Z_{p.d.}} (V_{inv} - V_t)^2 = \frac{1}{Z_{p.u.}} (-V_{td})^2$$

whence

$$V_{inv} = V_t - \frac{V_{td}}{\sqrt{Z_{p.u.}/Z_{p.d.}}}$$

The typical, values for Vt, Vinv and Vtd are

$$V_t = 0.2V_{DD}$$

;  $V_{td} = -0.6V_{DD}$

$V_{inv} = 0.5V_{DD}$  (for equal margins)

Substituting these values in the above equation ,we get

$$0.5 = 0.2 + \frac{0.6}{\sqrt{Z_{p.u.}/Z_{p.d.}}}$$

Here

$$\sqrt{Z_{p.u.}/Z_{p.d.}}=2$$

So, we get

$$Z_{p.u.}/Z_{p.d.} = 4/1$$

This is the ratio for pull-up to pull down ratio for an inverter directly driven by another inverter.

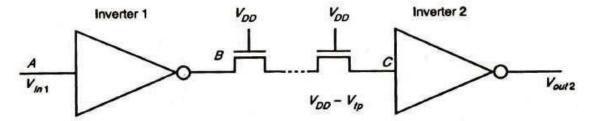

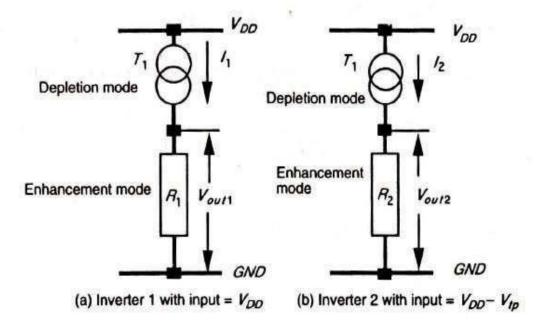

## Pull -Up to Pull-Down ratio for an nMOS Inverter driven through one or more Pass Transistors

Let us consider an arrangement in which the input to inverter 2 comes from the output of inverter 1

but passes through one or more nMOS transistors as shown in Fig. below (These transistors are called pass transistors).

The connection of pass transistors in series will degrade the logic 1 level / into inverter 2 so that the output will not be a proper logic 0 level. The critical condition is , when point A is at 0 volts and B is thus at VDD. but the voltage into inverter 2at point C is now reduced from VDD by the threshold voltage of the series pass transistor. With all pass transistor gates connected to VDD there is a loss of Vtp, however many are connected in series, since no static current flows through them and there can be no voltage drop in the channels. Therefore, the input voltage to inverter 2 is

Vin2 = VDD- Vtp where Vtp = threshold voltage for a pass transistor.

Let us consider the inverter 1 shown in Fig.(a) with input = VDD· If the input is at VDD, then the pull-down transistor T2 is conducting but with a low voltage across it; therefore, it is in its resistive region represented by R1 in Fig.(a) below. Meanwhile, the pull up transistor T1 is in saturation and is represented as a current source.

For the pull down transistor

$$R_{1} = \frac{V_{ds1}}{I_{ds}} = \frac{1}{K} \frac{L_{p.d.1}}{W_{p.d.1}} \left( \frac{1}{V_{DD} - V_{t} - \frac{V_{ds1}}{2}} \right)$$

$$I_{ds} = K \frac{W_{p.d.1}}{L_{p.d.1}} \left( (V_{DD} - V_{t}) V_{ds1} - \frac{V_{ds1}^{2}}{2} \right)$$

Since Vds is small, Vds/2 can be neglected in the above expression.

So,

$$R_1 \neq \frac{1}{K} Z_{p.d.1} \left( \frac{1}{V_{DD} - V_t} \right)$$

Now, for depletion mode pull-up transistor in saturation with Vgs = 0

$$I_1 = I_{ds} = K \frac{W_{p.u.1}}{L_{p.u.1}} \frac{(-V_{td})^2}{2}$$

The product  $1R1 = V_{out}1S_{o}$ ,

$$V_{out1} = I_1 R_1 = \frac{Z_{p.d.1}}{Z_{p.u.1}} \left( \frac{1}{V_{DD} - V_t} \right) \frac{(V_{ud})^2}{2}$$

Let us now consider the inverter 2 Fig.b .when input =  $V_{DD}$ -  $V_{tp}$ .

$$R_2 \neq \frac{1}{K} Z_{p.d.2} \frac{1}{((V_{DD} - V_{tp}) - V_t)}$$

$$I_2 = K \frac{1}{Z_{p,u,2}} \frac{(-V_{ul})^2}{2}$$

Whence,

$$V_{out 2} = I_2 R_2 = \frac{Z_{p.d.2}}{Z_{p.u.2}} \left( \frac{1}{V_{DD} - V_{tp} - V_t} \right) \frac{(-V_{td})^2}{2}$$

If inverter 2 is to have the same output voltage under these conditions then  $V_{out1} = V_{out2}$ . That is

I1R1=I2R2 , therefore

$$\frac{Z_{p.u.2}}{Z_{p.d.2}} = \frac{Z_{p.u.1}}{Z_{p.d.1}} \frac{(V_{DD} - V_t)}{(V_{DD} - V_{tp} - V_t)}$$

Considering the typical values

$$V_{tp} = 0.2V_{DD}$$

$$V_{tp} = 0.3V_{DD}^*$$

$$\frac{Z_{p.u.2}}{Z_{p.d.2}} = \frac{Z_{p.u.1}}{Z_{p.d.1}} \frac{0.8}{0.2}$$

Therefore

$$\frac{Z_{p.u.2}}{Z_{p.d.2}} \neq 2 \frac{Z_{p.u.1}}{Z_{p.d.1}} = \frac{8}{1}$$

From the above theory it is clear that, for an n-MOS transistor

- (i). An inverter driven directly from the output of another should have a  $Z_{p.u}/Z_{pd}$  ratio of  $\geq$  4/1.

- (ii). An inverter driven through one or more pass transistors should have a  $Z_{p.u.}/Z_{p.d}$  ratio of  $\geq 8/1$

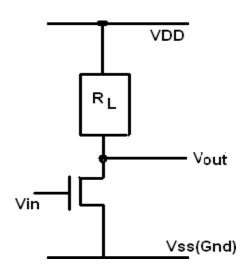

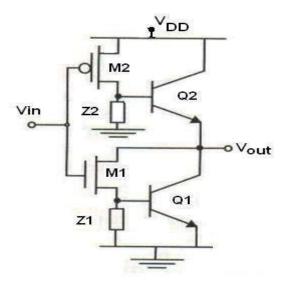

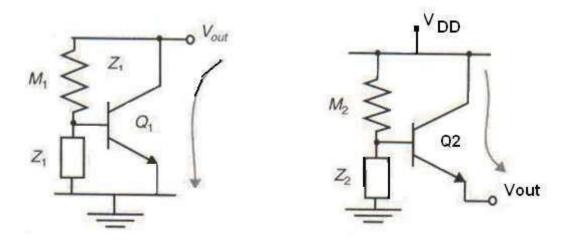

### ALTERMTIVE FORMS OF PULL -UP

Generally the inverter circuit will have a depletion mode pull-up transistor as its load. But there are also other configurations .Let us consider four such arrangements.

(i).Load resistance RL: This arrangement consists of a load resistor as apull-up as shown in the diagram below.But it is not widely used because of the large space requirements of resistors produced in a silicon substrate.

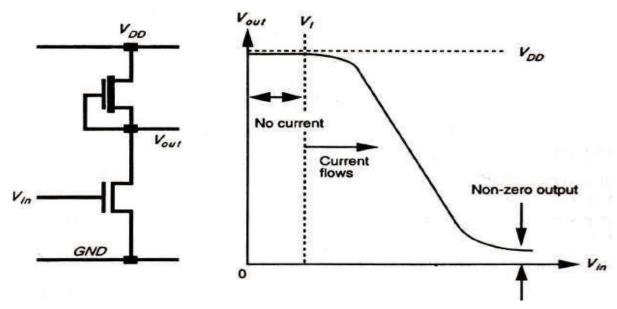

**nMOS depletion mode transistor pull-up**: This arrangement consists of a depletion mode transistor as pull-up. The arrangement and the transfer characteristic are shown below. In this type of arrangement we observe

- (a) Dissipation is high, since rail to rail current flows when Vin = logical 1.

- (b) Switching of output from 1 to 0 begins when Vin exceeds Vt, of pull-down device.

### nMOS depletion mode transistor pull-up and transfer characteristic

- (c) When switching the output from 1 to 0, the pull-up device is non-saturated initially and this presents lower resistance through which to charge capacitive loads.

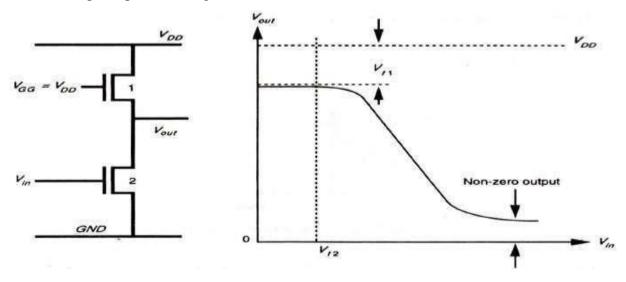

- (ii) **nMOS enhancement mode pull-up :**This arrangement consists of a n-MOS enhancement mode transistor as pull-up. The arrangement and the transfer characteristic are shown below.

### nMOS enhancement mode pull-up and transfer characteristic

The important features of this arrangement are

- (a) Dissipation is high since current flows when Vin =logical 1 (VGG is returned to VDD).

- (b) Vout can never reach VDD (logical I) if VGG = VDD as is normally the case.

- (c) VGG may be derived from a switching source, for example, one phase of a clock, so that

dissipation can be greatly reduced.

- (d) If VGG is higher than VDD then an extra supply rail is required.

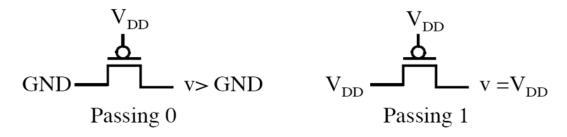

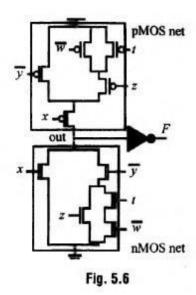

- (iii) **Complementary transistor pull-up (CMOS):** This arrangement consists of a C-MOS arrangement as pull-up. The arrangement and the transfer characteristic are shown below

### The salient features of this arrangement are

- (a) No current flows either for logical 0 or for logical 1 inputs.

- (b) Full logical 1 and 0 levels are presented at the output.

- (c) For devices of similar dimensions the p-channel is slower than the n-channel device.

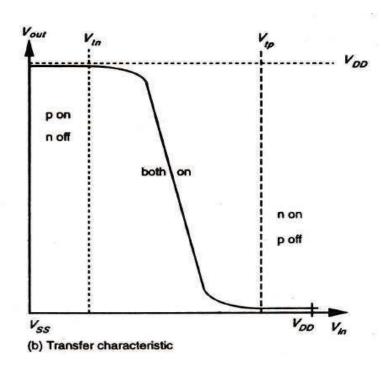

### **BICMOS INVERTER:**

A BiCMOS inverter, consists of a PMOS and NMOS transistor (M2 and M1), two NPN bipolar junction transistors, (Q2 and Q1), and two impedances which act as loads (Z2 and Z1) as shown in the circuit below.

When input, Vin, is high (VDD), the NMOS transistor (M1), turns on, causing Q1 to conduct, while M2 and Q2 are off, as shown in figure (b). Hence, a low (GND) voltage is translated to the output Vout. On the other hand, when the input is low, the M2 and Q2 turns on, while M1 and Q1 turns off, resulting to a high output level at the output as shown in Fig.(b).

In steady-state operation, Q1 and Q2 never turns on or off simultaneously, resulting to a lower power consumption. This leads to a push-pull bipolar output stage. Transistors M1 and M2, on the other hand, works as a phase-splitter, which results to a higher input impedance.

The impedances Z2 and Z1 are used to bias the base-emitter junction of the bipolar transistor and to ensure that base charge is removed when the transistors turn off. For example when the input voltage makes a high-to-low transition, M1 turns off first. To turn off Q1, the base charge must be removed, which can be achieved by Z1. With this effect, transition time reduces. However,

there exists a short time when both Q1 and Q2 are on, making a direct path from the supply (VDD) to the ground. This results to a current spike that is large and has a detrimental effect on both the noise and power consumption, which makes the turning off of the bipolar transistor fast.

### Comparison of BiCMOS and C-MOS technologies

The BiCMOS gates perform in the same manner as the CMOS inverter in terms of power consumption, because both gates display almost no static power consumption.

When comparing BiCMOS and CMOS in driving small capacitive loads, their performance are comparable, however, making BiCMOS consume more power than CMOS. On the other hand, driving larger capacitive loads makes BiCMOS in the advantage of consuming less power than CMOS, because the construction of CMOS inverter chains are needed to drive large capacitance loads, which is not needed in BiCMOS.

The BiCMOS inverter exhibits a substantial speed advantage over CMOS inverters, especially when driving large capacitive loads. This is due to the bipolar transistor's capability of effectively multiplying its current.

For very low capacitive loads, the CMOS gate is faster than its BiCMOS counterpart due to small values of *Cint*. This makes BiCMOS ineffective when it comes to the implementation of internal gates for logic structures such as ALUs, where associated load capacitances are small.

BiCMOS devices have speed degradation in the low supply voltage region and also BiCMOS is having greater manufacturing complexity than CMOS.

### **Assignment Ouestions:**

- 1. Define threshold voltage? Drive the Vt equation for MOS transistor.

- 2. Explain with neat diagrams the various NMOS fabrication technology.

- 3. Draw and explain BiCMOS inverter circuit.

- 4. Discuss the Basic Electrical Properties of MOS and BiCMOS Circuits.

- 5. Derive the expression for estimation of Pull-Up to Pull-Down ratio of an n-MOS inverter driven by another n-MOS inverter.

- 6. Derive the relationship between  $I_{ds}$  and  $V_{ds}$

- 7. Derive the expression for transfer characteristics of CMOS Inverter.

- 8. Write about BiCMOS fabrication in a n-well process with a diagram.

- 9. Distinguish between Bipolar and CMOS devices technologies in brief.

- 10. Mention about the BICMOS Inverters and alternative BICMOS Inverters.

- 11. Determine the pull-up to pull down ratio for NMOS inverter driven by another NMOS Inverter

- 12. Draw the fabrication steps of CMOS transistor and explain its operation in detail.

- 13. Draw the fabrication steps of NMOS transistor and explain its operation in detail.

# **UNIT II**

## **VLSI Circuit Design Processes**

- VLSI Design Flow

- MOS Layers

- Stick Diagrams

- Design Rules and Layout

- Lamda ( $\lambda$ ) based design rules for wires, contacts and Transistors

- Layout Diagrams for NMOS and CMOS Inverters and Gates

- Scaling of MOS circuits

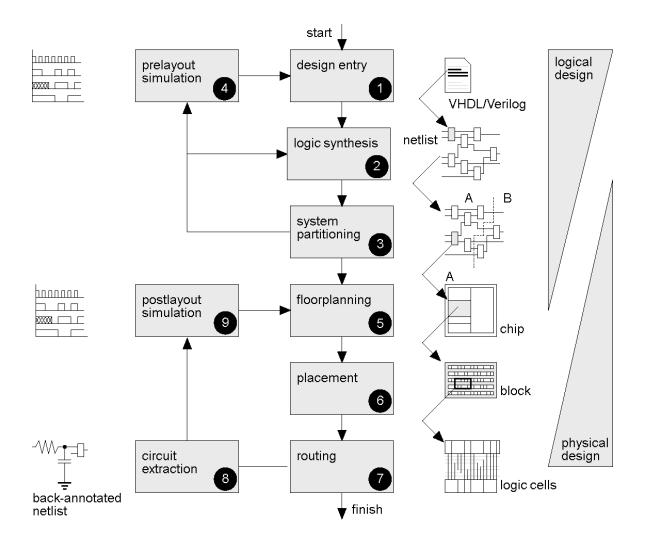

## **VLSI DESIGN FLOW**

A design flow is a sequence of operations that transform the IC designers' intention (usually represented in RTL format) into layout GDSII data.

A well-tuned design flow can help designers go through the chip-creation process relatively smoothly and with a decent chance of error-free implementation. And, a skilful IC implementation engineer can use the design flow creatively to shorten the design cycle, resulting in a higher likelihood that the product will catch the market window.

### Front-end design (Logical design):

- **1. Design entry** Enter the design in to an ASIC design system using a hardware description language (HDL) or schematic entry

- **2. Logic synthesis** Generation of net list (logic cells and their connections) from HDL code. Logic synthesis consists of following steps: (i) Technology independent Logic optimization (ii) Translation: Converting Behavioral description to structural domain (iii) Technology mapping or Library binding

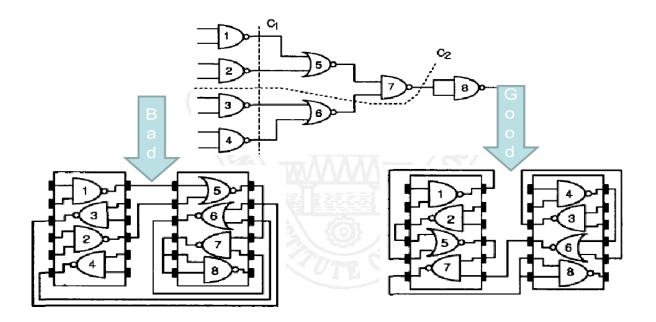

- **3. System partitioning** Divide a large system into ASIC-sized pieces

- **4. Pre-layout simulation** Check to see if the design functions correctly. Gate level functionality and timing details can be verified.

### **Back-end design (Physical design):**

- **5. Floor planning** Arrange the blocks of the netlist on the chip

- **6. Placement** Decide the locations of cells in a block

- 7. Routing Make the connections between cells and blocks

- **8. Circuit Extraction** Determine the resistance and capacitance of the interconnect

- **9. Post-layout simulation** Check to see the design still works with the added loads of the interconnect

### **Partitioning**

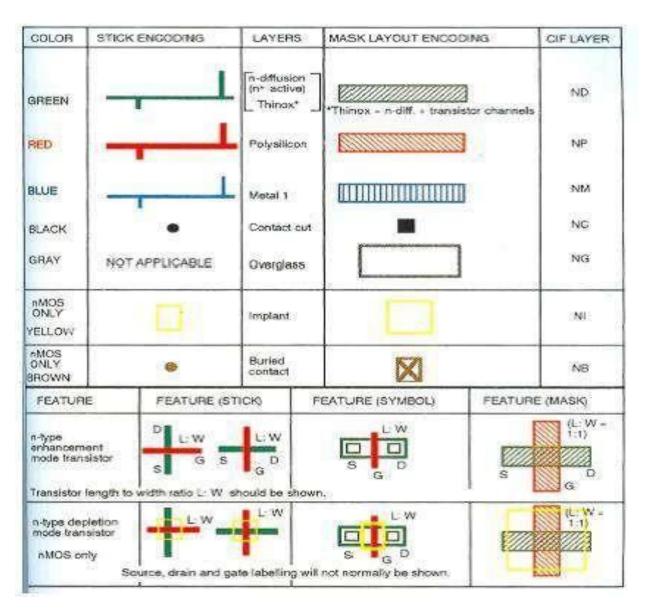

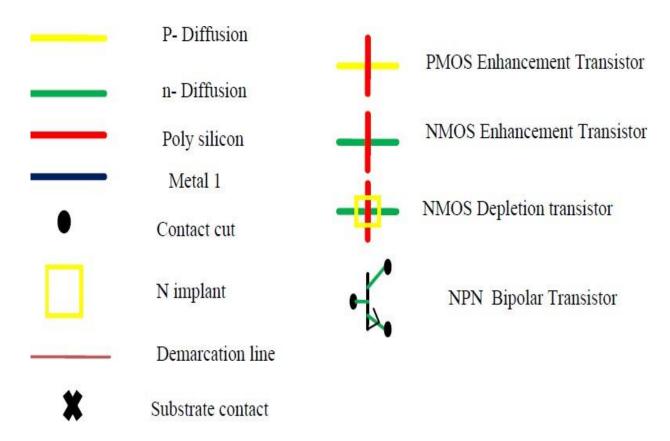

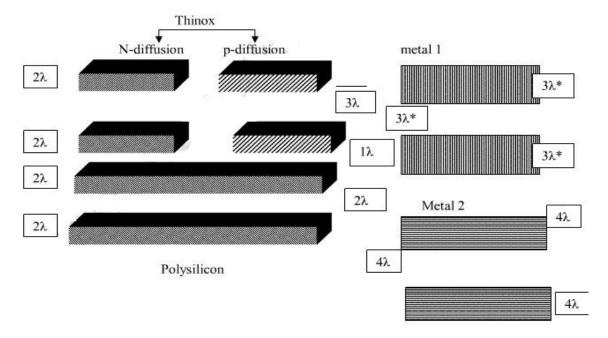

### MOS LAYERS

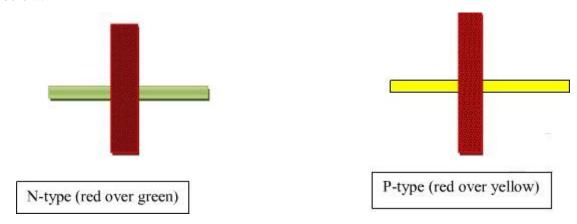

MOS design is aimed at turning a specification into masks for processing silicon to meet the specification. We have seen that MOS circuits are formed on four basic layers

- N-diffusion

- P-diffusion

- Poly Si

- Metal

which are isolated from one another by thick or thin (thinox) silicon silicon dioxide insulating layers. The thin oxide (thinox) mask region includes n-diffusion, p-diffusion, and transistor channels. Polysilicon and thinox regions interact so that a transistor is formed where they cross one another.

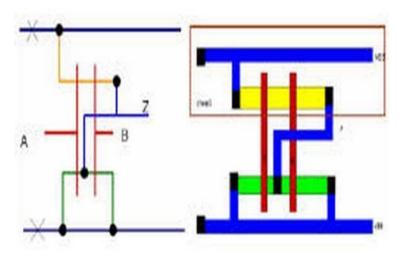

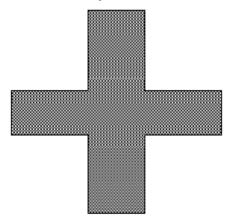

### STICK DIAGRAMS

A stick diagram is a diagrammatic representation of a chip layout that helps to abstract a model for design of full layout from traditional transistor schematic. Stick diagrams are used to convey the layer information with the help of a color code.

### "A stick diagram is a cartoon of a layout."

The designer draws a freehand sketch of a layout, using colored lines to represent the various process layers such as diffusion, metal and polysilicon. Where polysilicon crosses diffusion, transistors are created and where metal wires join diffusion or polysilicon, contacts are formed.

For example, in the case of nMOS design,

- Green color is used for n-diffusion

- Red for polysilicon

- Blue for metal

- Yellow for implant, and black for contact areas.

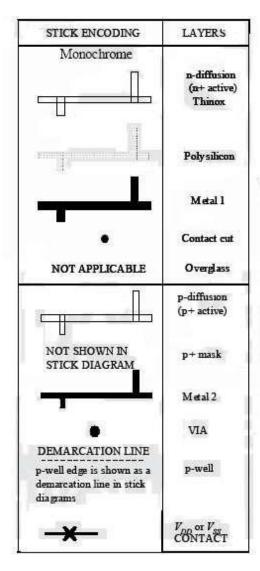

Monochrome encoding is also used in stick diagrams to represent the layer information.

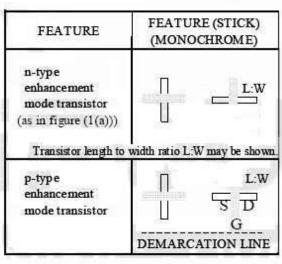

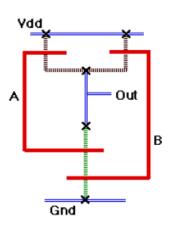

### Stick Diagrams -NMOS Encoding

NMOS ENCODING

### **CMOS ENCODING**

### <u>Stick Diagrams – Some Rules</u>

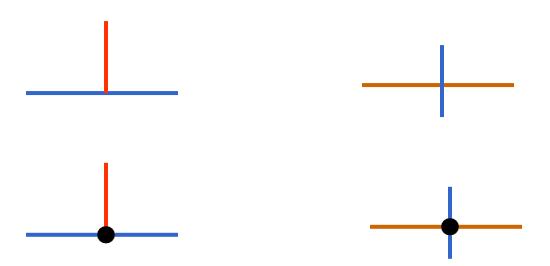

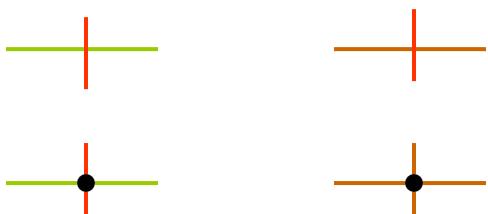

### Rule 1:

When two or more 'sticks' of the same type cross or touch each other that represents electrical contact.

### Rule 2:

When two or more "sticks" of different type cross or touch each other there is no electrical contact. (If electrical contact is needed we have to show the connection explicitly)

### **Rule 3:**

When a poly crosses diffusion it represents a transistor.

Note: If a contact is shown then it is **not** a transistor.

## Rule 4:

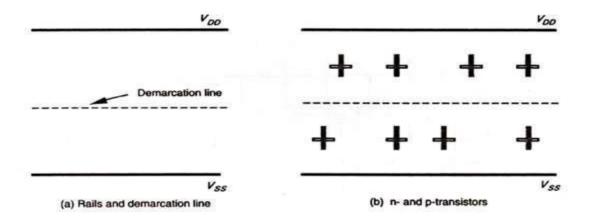

In CMOS a demarcation line is drawn to avoid touching of p-diff with n-diff. All PMOS must lie on one side of the line and all NMOS will have to be on the other side.

### nMOS Design Style:

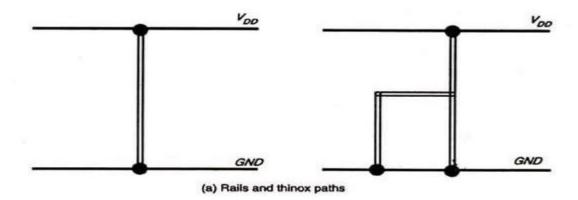

To understand the design rules for nMOS design style, let us consider a single metal, single polysilicon nMOS technology.

The layout of nMOS is based on the following important features.

- ✓ n-diffusion [n-diff.] and other thin oxide regions [thinox] (green);

- ✓ polysilicon 1 [poly.]-since there is only one polysilicon layer here (red);

- ✓ metal 1 [metal]-since we use only one metal layer here (blue);

- ✓ implant (yellow);

- ✓ contacts (black or brown [buried]).

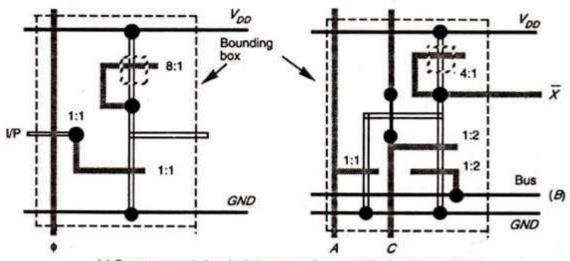

A transistor is formed wherever poly. crosses n-diff. (red over green) and all diffusion wires (interconnections) are n-type (green). When starting a layout, the first step normally taken is to draw the metal (blue) VDD and GND rails in parallel allowing enough space between them for the other circuit elements which will be required. Next, thinox (green) paths may be drawn between the rails for inverters and inverter based logic as shown in Fig. below. Inverters and inverter-based logic comprise a pull-up structure, usually a depletion mode transistor, connected from the output point to VDD and a pull down structure of enhancement mode transistors suitably interconnected between the output point and GND. This is illustrated in the Fig.(b). remembering that poly. (red) crosses thinox (green)wherever transistors are required. One should consider the implants (yellow) for depletion mode transistors and also consider the length to width (L:W) ratio for each transistor. These ratios are important particularly in nMOS and nMOS- like circuits.

(b) Pull-up and pull-down structures (polysilicon), implants, and ratios

(c) Buses, control signals, interconnections, and 'leaf-cell' boundaries

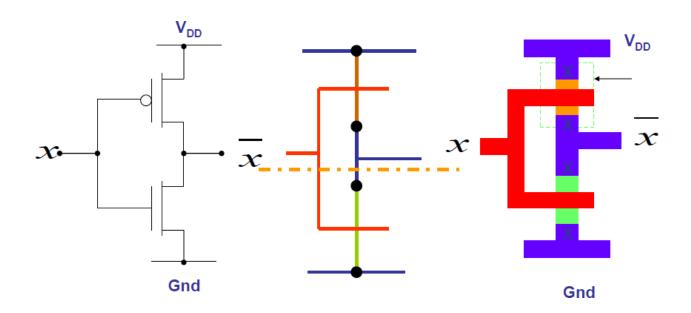

### **CMOS Design Style:**

The CMOS design rules are almost similar and extensions of n-MOS design rules except the Implant (yellow) and the buried contact (brown). In CMOS design Yellow is used to identify p transistors and wires, as depletion mode devices are not utilized. The two types of transistors 'n' and 'p', are separated by the demarcation line (representing the p-well boundary) above which all p-type devices are placed (transistors and wires (yellow). The n-devices (green) are consequently placed below the demarcation line and are thus located in the p-well as shown in the diagram below.

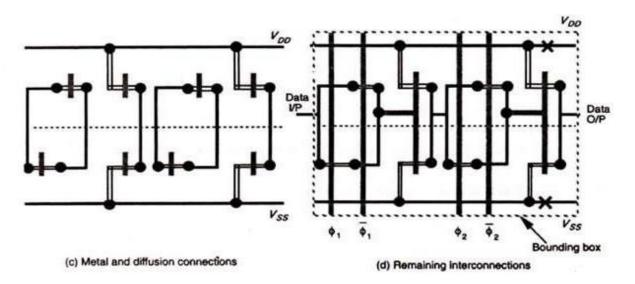

Diffusion paths must not cross the demarcation line and n-diffusion and p-diffusion wires must not join. The 'n' and 'p' features are normally joined by metal where a connection is needed. Their geometry will appear when the stick diagram is translated to a mask layout. However, one must not forget to place crosses on VDD and Vss rails to represent the substrate and p-well connection respectively. The design style is explained by taking the example the design of a single bit shift register. The design begins with the drawing of the VDD and Vss rails in parallel and in metal and the creation of an (imaginary) demarcation line in-between, as shown in Fig.below. The n-transistors are then placed below this line and thus close to Vss, while p-transistors are placed above the line and below VDD In both cases, the transistors are conveniently placed with their diffusion paths parallel to the rails (horizontal in the diagram) as shown in Fig.(b). A similar approach can be taken with transistors in symbolic form.

Fig. CMOS stick layout design style (a,b,c,d)

The n- along with the p-transistors are interconnected to the rails using the metal and connect as Shown in Fig.(d). It must be remembered that only metal and poly-silicon can cross the demarcation line but with that restriction, wires can run-in diffusion also. Finally, the remaining interconnections are made as appropriate and the control signals and data inputs are added as shown in the Fig.(d).

## **Stick Diagrams:**

**Buried Contact**

## **Examples of Stick Diagrams**

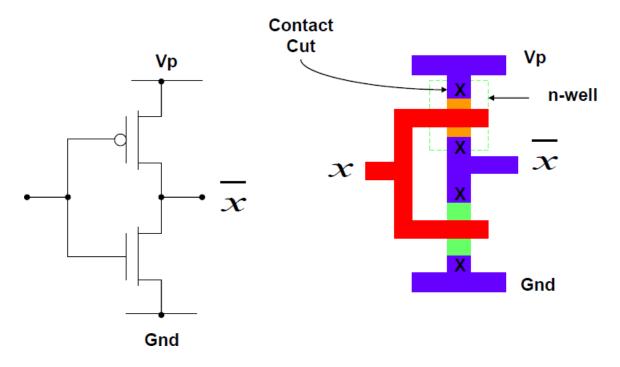

## **CMOS Inverter**

## Contd....

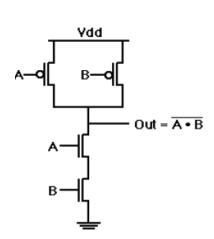

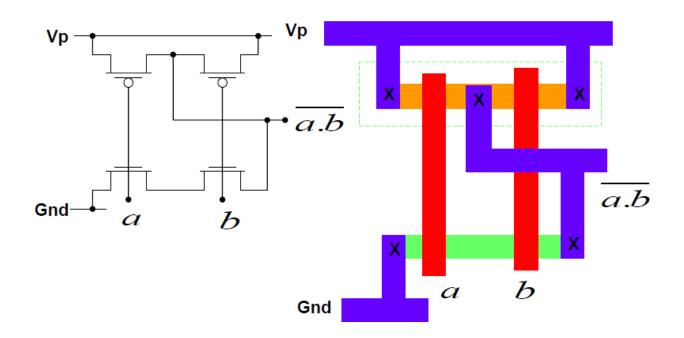

| Α | В | <b>A •</b> B |

|---|---|--------------|

| 0 | 0 | 1            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

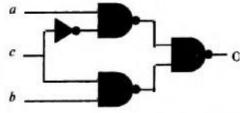

|   |   |              |

- 1. Pull-down: Connect to ground If A=1 AND B=1

- 2. Pull-up: Connect to Vdd If A=0 OR B=0

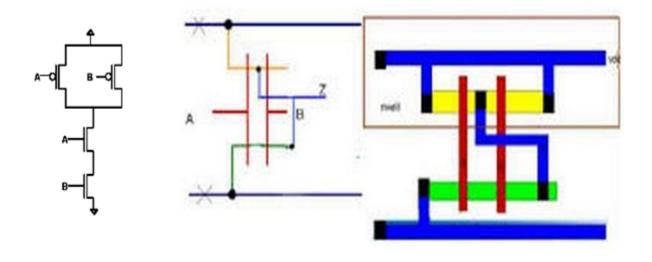

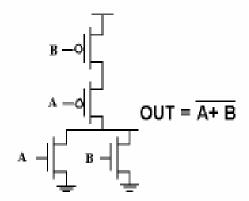

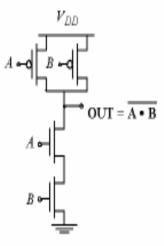

Fig. CMOS NAND gate

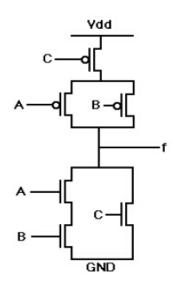

## Example: $f = \overline{(A \cdot B) + C}$

### **Design Rules and Layout**

In VLSI design, as processes become more and more complex, need for the designer to understand the intricacies of the fabrication process and interpret the relations between the different photo masks is really troublesome. Therefore, a set of layout rules, also called **design rules**, has been defined. They act as an interface or communication link between the circuit designer and the process engineer during the manufacturing phase. The objective associated with layout rules is to obtain a circuit with optimum yield (functional circuits versus non-functional circuits) in as small as area possible without compromising reliability of the circuit. In addition, Design rules can be conservative or aggressive, depending on whether yield or performance is desired. Generally, they are a compromise between the two. Manufacturing processes have their inherent limitations in accuracy. So the need of design rules arises due to manufacturing problems like –

- Photo resist shrinkage, tearing.

- Variations in material deposition, temperature and oxide thickness.

- Impurities.

- · Variations across a wafer.

These lead to various problems like:

#### • Transistor problems:

Variations in threshold voltage: This may occur due to variations in oxide thickness, ion-implantation and poly layer. Changes in source/drain diffusion overlap. Variations in substrate.

### • Wiring problems:

Diffusion: There is variation in doping which results in variations in resistance, capacitance. Poly, metal: Variations in height, width resulting in variations in resistance, capacitance. Shorts and opens.

### • Oxide problems:

Variations in height.

Lack of planarity.

### Via problems:

Via may not be cut all the way through.

Undersize via has too much resistance.

Via may be too large and create short.

To reduce these problems, the design rules specify to the designer certain geometric constraints on the layout artwork so that the patterns on the processed wafers will preserve the topology and geometry of the designs. This consists of minimum-width and minimum-spacing constraints and requirements between objects on the same or different layers. Apart from following a definite set of rules, design rules also come by experience.

### Why we use design rules?

- Interface between designer and process engineer

- Historically, the process technology referred to the length of the silicon channel between the source and drain terminals in field effect transistors.

- The sizes of other features are generally derived as a ratio of the channel length, where some may be larger than the channel size and some smaller.

For example, in a 90 nm process, the length of the channel may be 90 nm, but the width of the gate terminal may be only 50 nm.

```

<u>Semiconductor</u>

manufacturing

processes

10 µm — 1971

3 <u>µm</u> — 1975

1.5 µm — 1982

<u>1 µm</u> — 1985

800 nm (ο.8ο μm) — 1989

600 nm (0.60 μm) - 1994

350 nm (0.35 µm) - 1995

250 nm (0.25 µm) - 1998

180 nm (0.18 \, \mu m) - 1999

130 nm (0.13 μm) — 2000

90 nm - 2002

65 nm - 2006

45 nm - 2008

32 nm - 2010

22 nm — approx. 2011

16 nm — approx. 2018

11 nm — approx. 2022

```

Design rules define ranges for features

### Examples:

- min. wire widths to avoid breaks

- min. spacing to avoid shorts

- minimum overlaps to ensure complete overlaps

- Measured in microns

- Required for resolution/tolerances of masks

Fabrication processes defined by minimum channel width

- Also minimum width of poly traces

- Defines "how fast" a fabrication process is

## **Types of Design Rules**

The design rules primary address two issues:

- 1. The geometrical reproduction of features that can be reproduced by the maskmaking and lithographical process, and

- 2. The interaction between different layers.

There are primarily two approaches in describing the design rules.

- 1. Linear scaling is possible only over a limited range of dimensions.

- 2. Scalable design rules are conservative . This results in over dimensioned and less dense design.

- 3. This rule is not used in real life.

### 1. Scalable Design Rules (e.g. SCMOS, λ-based design rules):

In this approach, all rules are defined in terms of a single parameter  $\lambda$ . The rules are so chosen that a design can be easily ported over a cross section of industrial process ,making the layout portable .Scaling can be easily done by simply changing the value of.

The key disadvantages of this approach are:

### 2. Absolute Design Rules (e.g. μ-based design rules ):

In this approach, the design rules are expressed in absolute dimensions (e.g.  $0.75\mu m$ ) and therefore can exploit the features of a given process to a maximum degree. Here, scaling and porting is more demanding, and has to be performed either manually or using CAD tools .Also, these rules tend to be more complex especially for deep submicron.

The fundamental unity in the definition of a set of design rules is the minimum line width .It stands for the minimum mask dimension that can be safely transferred to the semiconductor material .Even for the same minimum dimension, design rules tend to differ from company to company, and from process to process. Now, CAD tools allow designs to migrate between compatible processes.

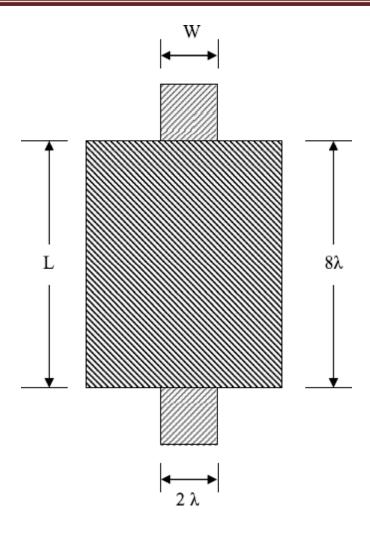

### LAMBDA-BASED DESIGN RULES:-

- Lambda-based (scalable CMOS) design rules define scalable rules based on  $\lambda$  (which is half of the minimum channel length)

- classes of MOSIS SCMOS rules: SUBMICRON, DEEPSUBMICRON

- Stick diagram is a draft of real layout, it serves as an abstract view between the schematic and layout.

- Circuit designer in general want tighter, smaller layouts for improved performance and decreased silicon area.

- On the other hand, the process engineer wants design rules that result in a controllable and reproducible process.

- Generally we find there has to be a compromise for a competitive circuit to be produced at a reasonable cost.

- All widths, spacing, and distances are written in the form

- $\lambda = 0.5 \text{ X}$  minimum drawn transistor length

- Design rules based on single parameter,  $\lambda$

- Simple for the designer

- Wide acceptance

- Provide feature size independent way of setting out mask

- If design rules are obeyed, masks will produce working circuits

- Minimum feature size is defined as 2  $\lambda$

- Used to preserve topological features on a chip

- Prevents shorting, opens, contacts from slipping out of area to be contacted

## LAMBDA BSED RULES

### MINIMUM WIDTH AND SPACING RULES

| LAYER         | TYPE OF RULE                     | VALUE    |

|---------------|----------------------------------|----------|

| POLY          | Minimum Width<br>Minimum Spacing | 2λ<br>2λ |

| N/P DIFFUSION | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| N-WELL        | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| P-WELL        | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

| METAL1        | Minimum Width<br>Minimum Spacing | 3λ<br>3λ |

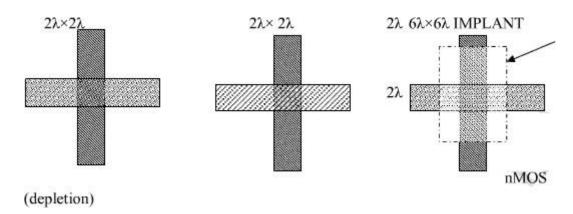

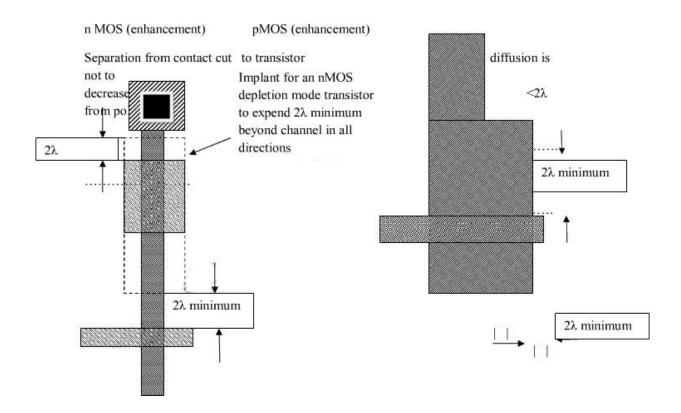

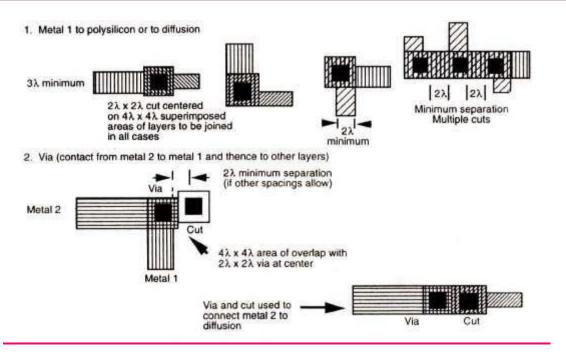

### **DESIGN RULES FOR WIRES (nMOS and CMOS)**

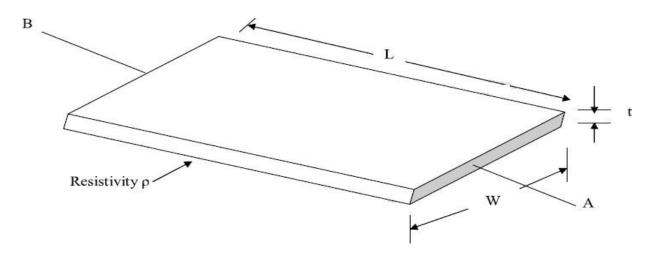

Design rules and layout methodology based on the concept of  $\lambda$  provide a process and feature size independent way of setting out mask dimensions to scale. All paths in layers are dimensioned in  $\lambda$  units and subsequently  $\lambda$  can be allocated an appropriate value compatible with the feature size of the fabrication process.

Minimum width minimum separation (where specified)

polysilicon to extend a minimum of 2λ beyond diffusion boundaries (width constant)

Separation from implant to another transistor

Key: polysilicon p-diffusion p-diffusion transistor

(Polysilicon over thinox)

channel

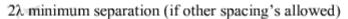

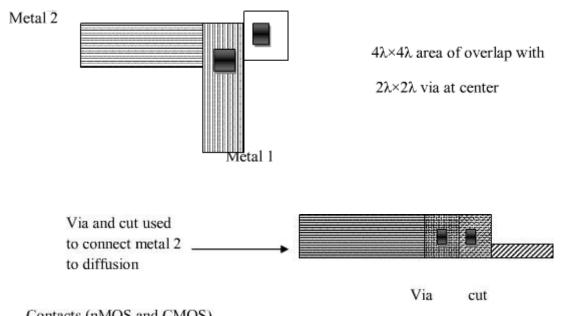

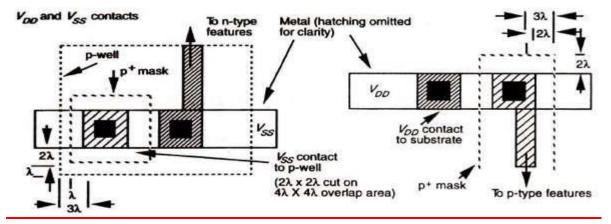

$2\lambda \times 2\lambda$  cut centered on  $4\lambda \times 4\lambda$  superimposed area of layers to be joined in all cases

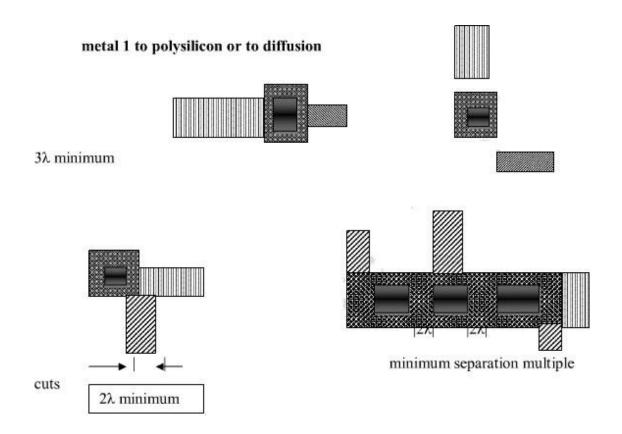

Contacts (nMOS and CMOS)

### **CONTACT CUTS**

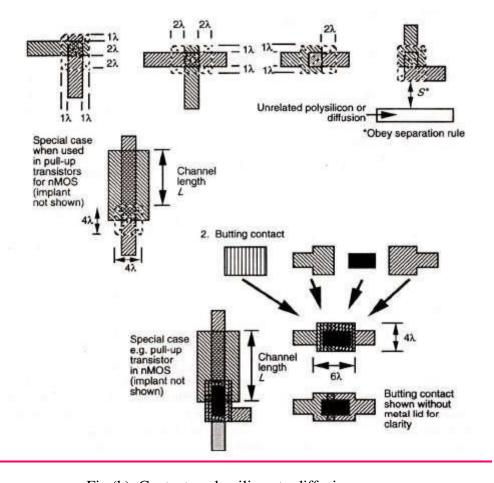

When making contacts between poly-silicon and diffusion in nMOS circuits it should be remembered that there are three possible approaches--poly. to metal then metal to diff., or aburied contact poly. to diff. , or a butting contact (poly. to diff. using metal). Among the three the latter two, the buried contact is the most widely used, because of advantage in space and a reliable contact. At one time butting contacts were widely used , but now a days they are superseded by buried contacts.

In CMOS designs, poly. to diff. contacts are always made via metal. A simple process is followed for making connections between metal and either of the other two layers (as in Fig.a), The  $2\lambda$ . x  $2\lambda$ . contact cut indicates an area in which the oxide is to be removed down to the underlying polysilicon or diffusion surface. When deposition of the metal layer takes place the metal is deposited through the contact cut areas onto the underlying area so that contact is made between the layers.

The process is more complex for connecting diffusion to poly-silicon using the butting contact approach (Fig.b), In effect, a  $2\lambda$ . x  $2\lambda$  contact cut is made down to each of the layers to be joined. The layers are butted together in such a way that these two contact cuts become contiguous. Since the poly-silicon and diffusion outlines overlap and thin oxide under poly silicon acts as a mask in the diffusion process, the poly-silicon and diffusion layers are also butted together. The contact between the two butting layers is then made by a metal overlay as shown in the Fig.

Fig.(a) . n-MOS & C-MOS Contacts

Fig.(b). Contacts poly-silicon to diffusion

In buried contact basically, layers are joined over a  $2\lambda$ . x  $2\lambda$ . area with the buried contact cut extending by  $1\lambda$ , in all directions around the contact area except that the contact cut extension is increased to  $2\lambda$ . in diffusion paths leaving the contact area. This helps to avoid the formation of unwanted transistors. So this buried contact approach is simpler when compared to others. The, poly-silicon is deposited directly on the underlying crystalline wafer. When diffusion takes place, impurities will diffuse into the poly-silicon as well as into the diffusion region within the contact area. Thus a satisfactory connection between poly-silicon and diffusion is ensured. Buried contacts can be smaller in area than their butting contact counterparts and, since they use no metal layer, they are subject to fewer design rule restrictions in a layout.

## Other design rules

- Double Metal MOS process Rules

- CMOS fabrication is much more complex than nMOS fabrication

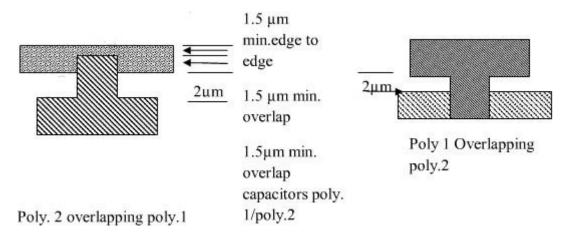

- 2 um Double metal, Double poly. CMOS/BiCMOS Rules

- 1.2um Double Metal single poly.CMOS rules

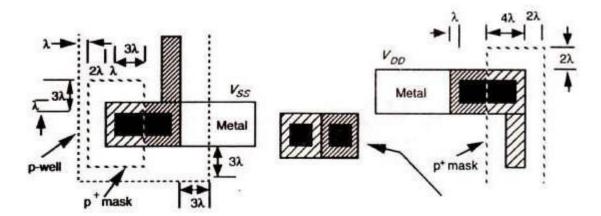

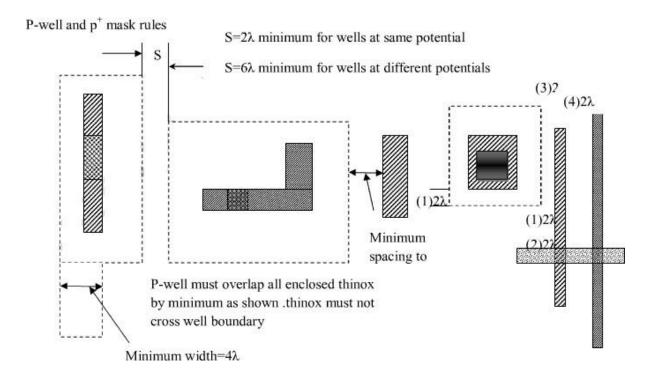

#### **CMOS Lambda-based Design Rules:**

The CMOS fabrication process is more complex than nMOS fabrication. In a CMOS process, there are nearly 100 actual set of industrial design rules. The additional rules are concerned with those features unique to p-well CMOS, such as the p-well and p+ mask and the special 'substrate contacts. The p-well rules are shown in the diagram below

In the diagram above each of the arrangements can be merged into single split contacts.

From the above diagram it is also clear that split contacts may also be made with separate cuts.

The CMOS rules are designed based on the extensions of the Mead and Conway concepts and also by excluding the butting and buried contacts the new rules for CMOS design are formed. These rules for CMOS design are implemented in the above diagrams.

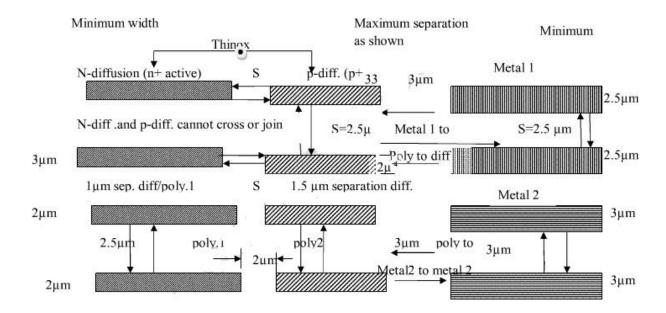

### uM CMOS Design rules

The encoding is compatible with that already described where as following extension are made: n-well brown

Poly 1 → red; poly 2 → orange; diff (n-active) → green; p Diff (p-active) → yellow.

For BiCMOS the following are

added: buried n+ sub collector- pale green; p-base--pink.

AVOID COINCIDENT EDGES WHERE METAL 1 AND METAL 2 RUNS FOLLOW THE SAME PATH FOR >25µm LENGTH (UNDER LAP METAL 1 Design rules for wires (interconnects) (orbit 2µm CMOS)

## 2µm DOUBLE METAL, SINGLE POLY CMOS RULES

$The\ orbit\ ^{TM}\ 1.2\mu m\ rules\ provide$  improved feature size. A separate set of micro based design rules accompany them

#### Design rules for wires (interconnects) (orbit 1.2 µm CMOS) Thino Minimum width Minimum separation as Minimum width shown n-diffusion (n+ active) 2.2µn 2µm S n-diff and p-diff. cannot cross or S=1.2um Metal 1 to 2µm metal 0.4 µm separation Diff. /poly 1.2µm Poly to ploy 2µm 1.8µm Polysilicon Metal 2 to 1.6 um metal2 1.2µm

Avoid coincident edges where metal 1 and metal2 runs follow the same path for>25μm length (under lap metal 1 edges by 0.8 μm).

2 µm

N-WELL AND ACTIVE AREA MASKS POLY MASK -> DEFINE NMOS

TRANSISTORS

Metal mask for VDD, GND and output connections

$V_A$ METAL -DIFFUSION CONSTANT MASK

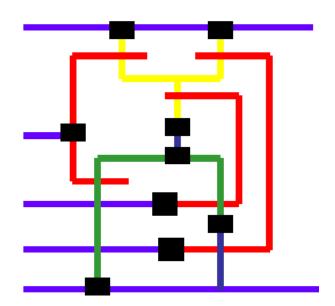

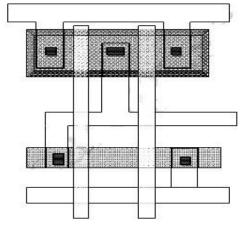

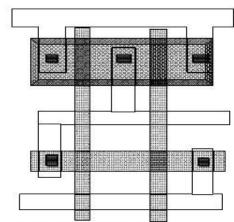

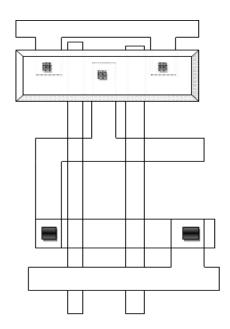

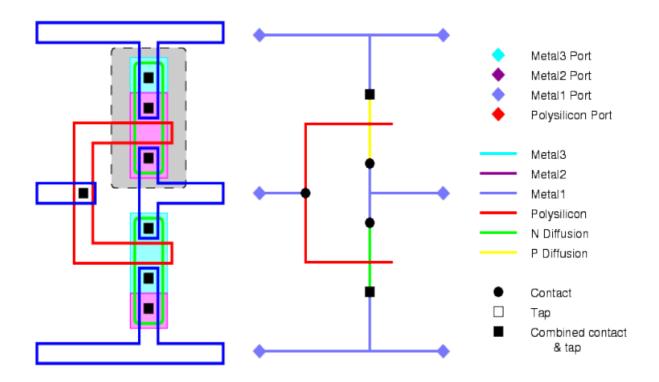

# **Layout Diagrams for NMOS and CMOS Inverters and Gates**

# **Layer Types**

- p-substrate

- n-well

- -n+

- -p+

- Gate oxide

- Gate (polysilicon)

- Field Oxide

- Insulated glass

- · Provide electrical isolation

# **Basic Gate Design**

Both the power supply and ground are routed using the Metal layer

n+ and p+ regions are denoted using the same fill pattern. The only difference is the n-well

Contacts are needed from Metal to n+ or p+

# The CMOS NOT Gate

# The CMOS NAND Gate

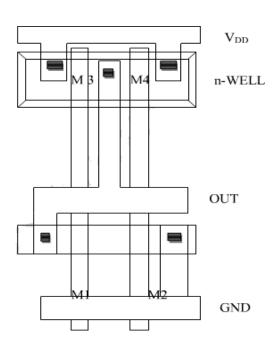

# **Layout & Stick Diagram of CMOS Inverter**

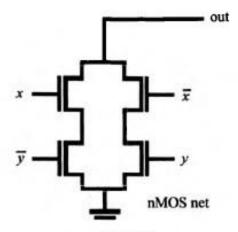

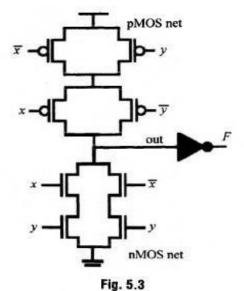

# 2 input NAND gate

#### Unit-2

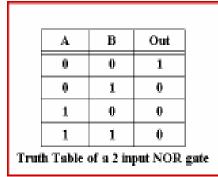

## 2 input NOR gate

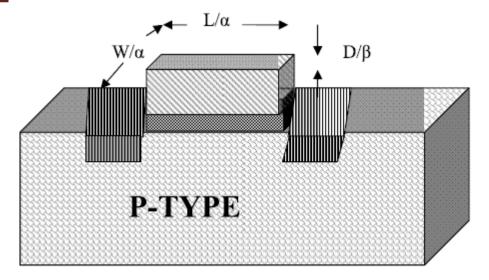

## **Scaling of MOS circuits**

Scaling means to reduce the feature size and to achieve higher packing density of circuitry on a chip, Many figures of merit such as minimum feature size, number of gates on one chip, power dissipation, maximum operational frequency, die size, production cost can be improved by shrinking the dimensions of transistors, interconnections and the separation between features, and by adjusting the doping levels and supply voltages.

## SCALING MODELS AND SCALING FACTORS:

The most commonly used models are the constant electric field scaling models and the constant voltage scaling model. One more model called as combined voltage and dimension scaling model is presented recently. The following figure indicates the device dimensions and substrate doping level which are associated with the scaling of a transistor.

Two scaling factors  $1/\alpha$ ,  $1/\beta$  are

used.  $1/\beta$  is chosen as the scaling factor for supply voltage  $V_{DD}$  and gate oxide thickness D, and  $1/\alpha$  is used for all other linear dimensions, both vertical and horizontal to chip surface.

#### SCALING FACTORS FOR DEVICE PARAMETERS:

## GATE AREA AG:

$$Ag = L.W$$

Where L and W are the channel length and width respectively, both are scaled by  $1/\alpha$ . So Ag is scaled by  $1/\alpha^2$

## GATE CAPACITANCE PER UNIT ARE Co OR Cox:

$$C_o = E_{OX}/D$$

Where  $E_{OX}$  is the permittivity of the gate oxide (thinox) (= $E_{ins}$ . $E_{O}$ ) and D is the gate oxide thickness which is scaled by  $1/\beta$

Thus  $C_0$  is scaled by  $1/1/\beta = \beta$

## GATE CAPACITANCE Cg:

Thus  $C_g$  is scaled by  $\beta.1/\alpha^2\!\!=\!\!\beta/\alpha^2$

## PARASITIC CAPACITANCE C<sub>X</sub>

$C_X$  is proportional to  $A_X/d$ .

Where d is the depletion width around source or drain which is scaled by  $1/\alpha$  and  $A_X$  is the area of depletion region around source or drain which is scaled by  $1/\alpha_2$ .  $1/1/\alpha = 1/\alpha$

## CARRIER DENSITY IN CHANNEL Qon

Where Qon is the average

charge per unit area in the channel in the 'on' state.  $C_o$  is scaled by  $\beta$  and  $V_{gs}$  is scaled by  $1/\beta$ .

Thus Qon is scaled by 1.

## CHANNEL RESISTANCE Ron

Where  $\mu$  is the carrier mobility in the channel and is assumed constant. Thus  $R_{on}$  is scaled by  $1/\alpha$ .  $1/1/\alpha=1$ .

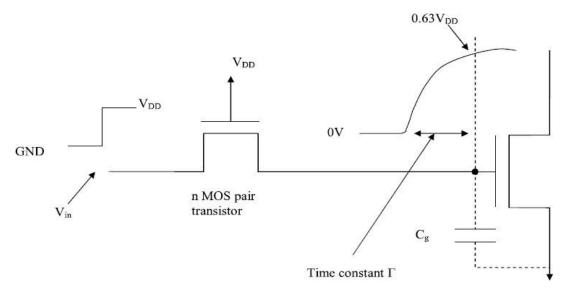

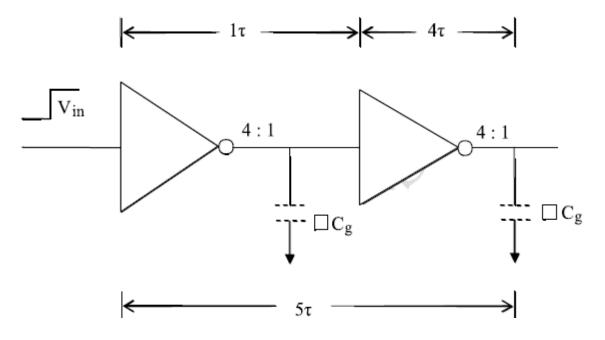

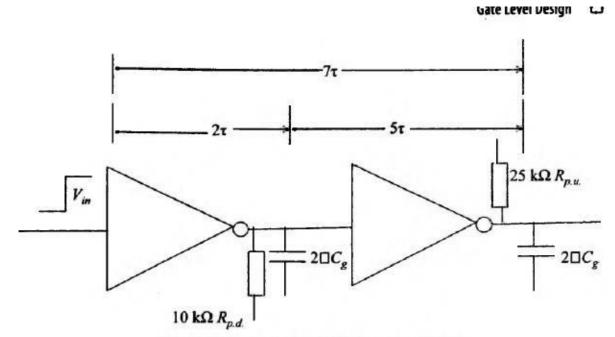

## GATE DELAY Td

## Td is proportional to Ron.Cg.

Thus  $T_d$  is scaled by  $\beta^2/\alpha^4$

## MAXIMUM OPERATING FREQUENCY Fo:

$$F_o = W/L *\mu C_O V_{DD}/Cg$$

Or  $f_o$  is inversely proportional to delay  $T_d.$  Thus  $f_o$  is scaled by  $1/\beta/\alpha^2 = \!\! \alpha^2/\beta$

#### SATURATION CURRENT IDSS:

$$I_{dss} = C_{o\mu}/2.W/L. (V_{gs}-V_t)^2$$

Nothing that both  $V_{gs}$  and  $V_t$  are

scaled by  $1/\beta$ , we have  $I_{dss}$  is scaled by  $\beta(1/\beta)^2=1/\beta$ .

#### **CURRENT DENSITY J:**

$$J=I_{des}/A$$