# **IC APPLICATIONS**

## NOTES

### **III BTECH, ECE**

## 1<sup>st</sup> SEMESTER(2022-23)

### R20

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## (UGC AUTONOMOUS)

Accredited by NAAC & NBA, Approved by AICTE, Permanently Affiliated to JNTUH

Bhaskar Nagar, Yenkapally (v), Moinabad (m),

Hyderabad-500075, Telangana, India

| AY 2020-21               | J. B. Institute of Engineering and Technology | <b>B.Tech: ECE</b> |   |   |   |                 |

|--------------------------|-----------------------------------------------|--------------------|---|---|---|-----------------|

| Onwards                  | (UGC Autonomous)                              | III Year – ISem    |   |   |   |                 |

| Course<br>Code:<br>J314C | IC APPLICATIONS                               | L                  | Т | Р | D |                 |

| Credits: 3               |                                               | 3                  | 0 | 0 | 0 | <u>Syllabus</u> |

Pre-requisite: Electronic devices and circuits

Switching Theory & Logic Design, Pulse & Digital Circuits

#### Course Objectives:

1. To introduce the basic building blocks of linear integrated circuits.

2. To teach the linear and non – linear applications of operational amplifiers.

3. To introduce the theory and applications of analog multipliers and PLL.

4. To introduce the concepts of waveform generation and introduce some special function ICs.

5.To understand and implement the working of basic digital circuits

#### MODULE 1:

#### **Unit 1: Introduction to Linear Integrated Circuits**

Ideal and Practical Op-Amp, Op-Amp Characteristics, DC and AC Characteristics, Features of 741 Op-Amp, Modes of Operation - Inverting, Non-Inverting, Differential

#### Unit 2: Non-Linear Applications of OP-AMP

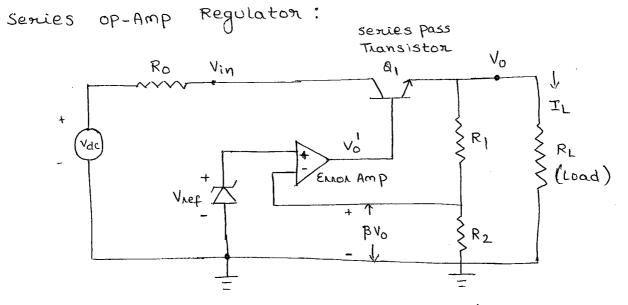

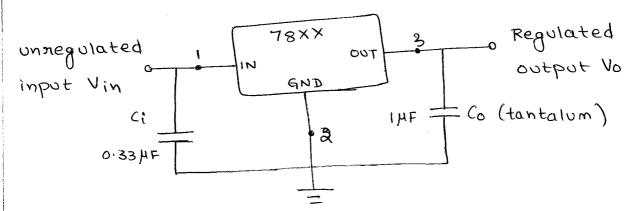

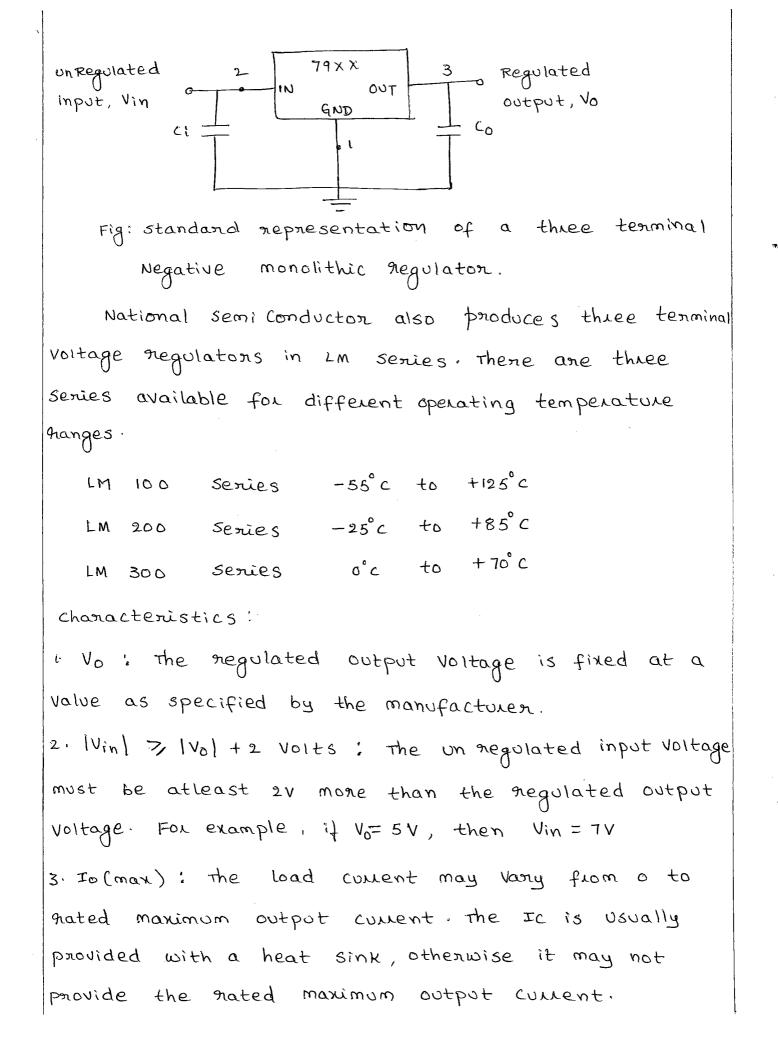

Instrumentation Amplifier, AC Amplifier, Differentiators and Integrators, Comparators, Schmitt Trigger, Introduction to Voltage Regulators, Features of 723 Regulator, Three Terminal Voltage Regulators.

#### MODULE 2:

#### **Unit 1: Introduction to IC-555 Applications**

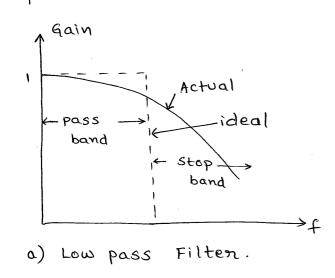

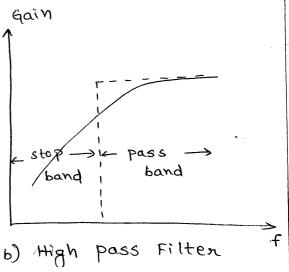

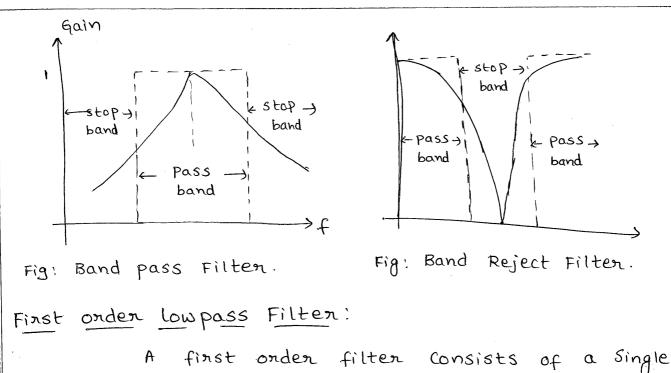

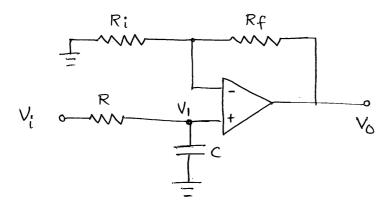

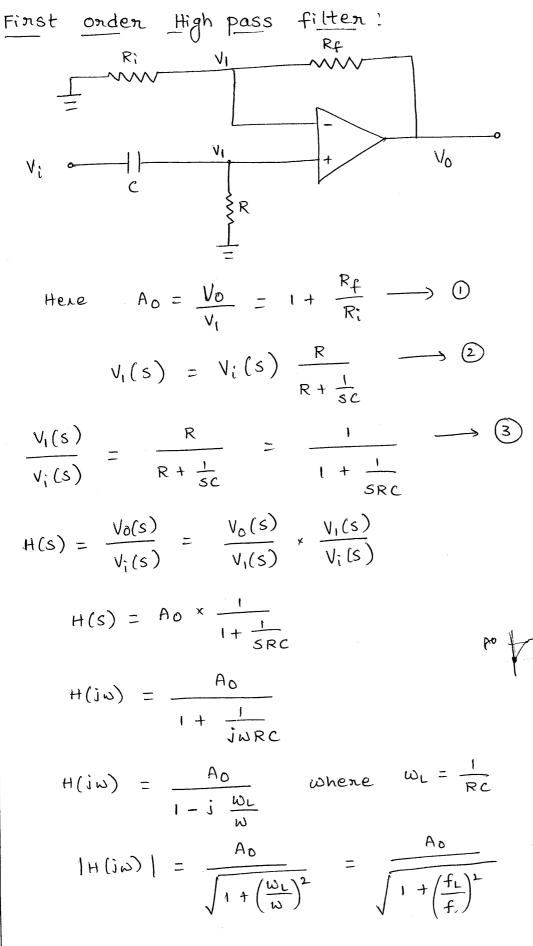

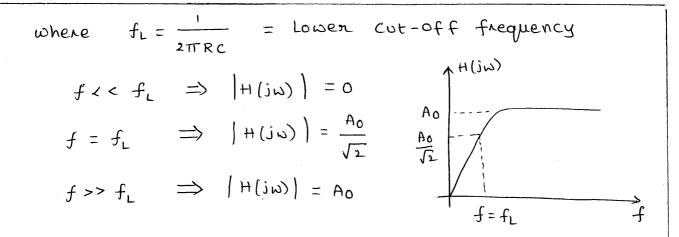

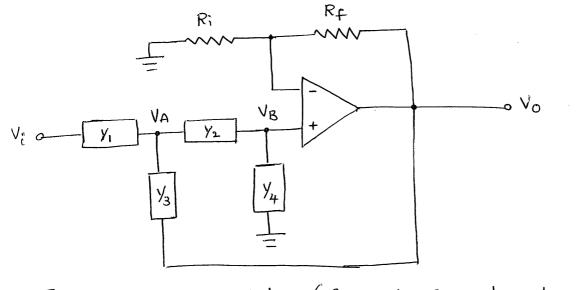

Introduction to Active Filters, Characteristics of Band pass, Band reject and All Pass Filters, Analysis of 1st order LPF & HPF Butterworth Filters, Waveform Generators – Triangular, Saw tooth, Square Wave, IC555 Timer -Functional Diagram, Monostable, and Astable Operations, Applications.

#### Unit 2: Timer and Phase Locked Loops(PLL)

Applications

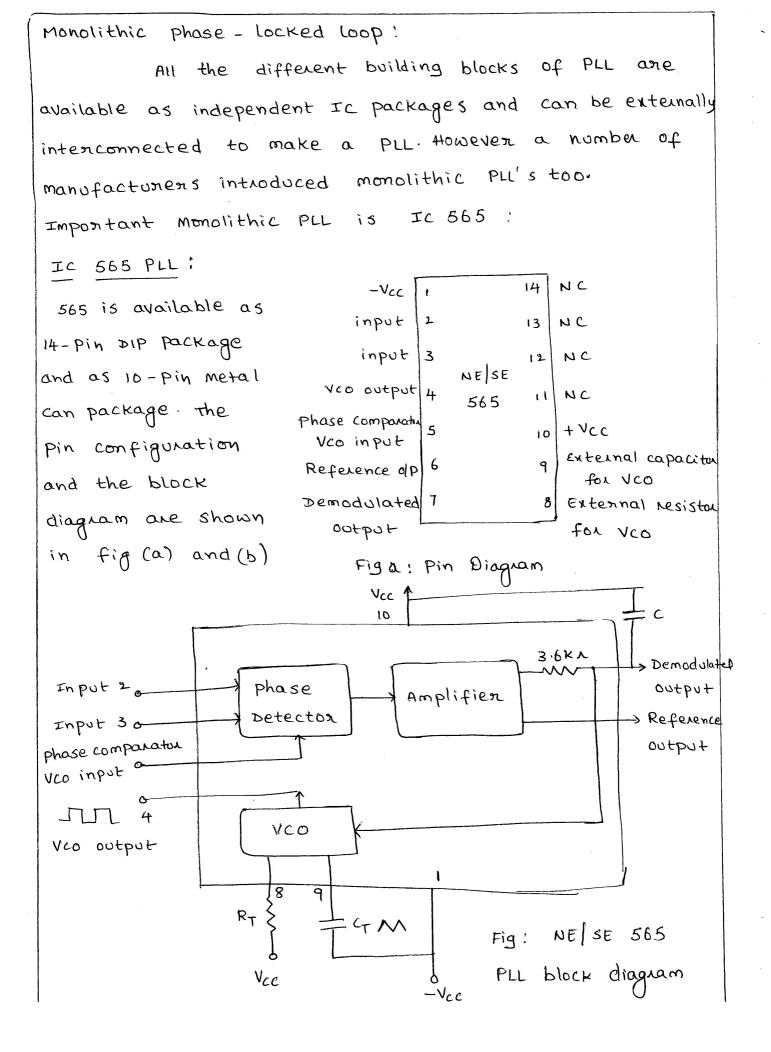

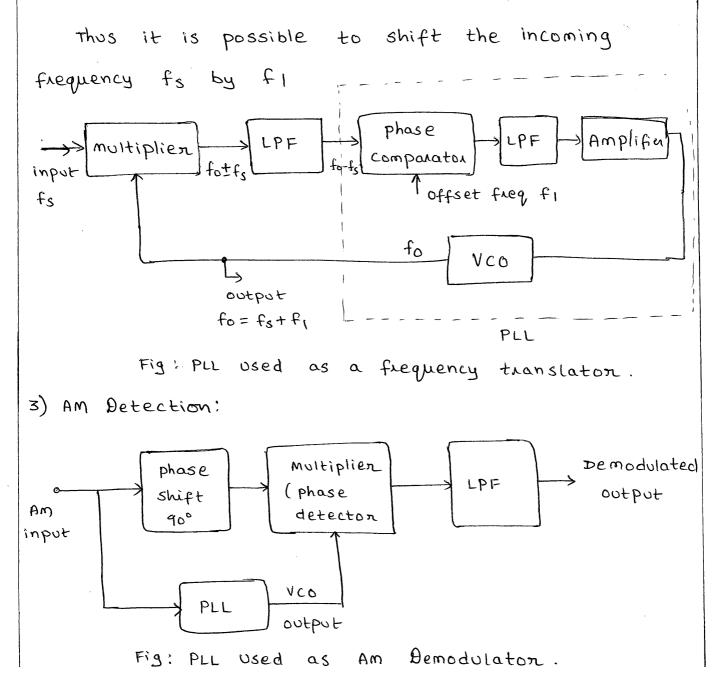

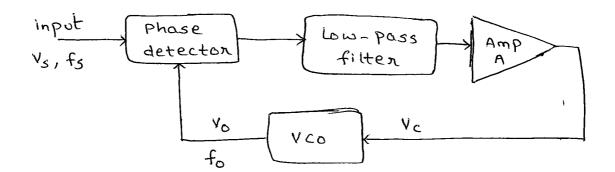

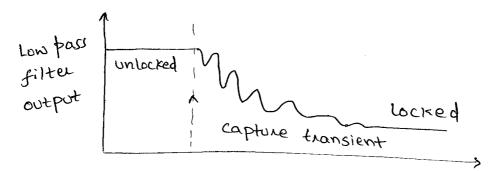

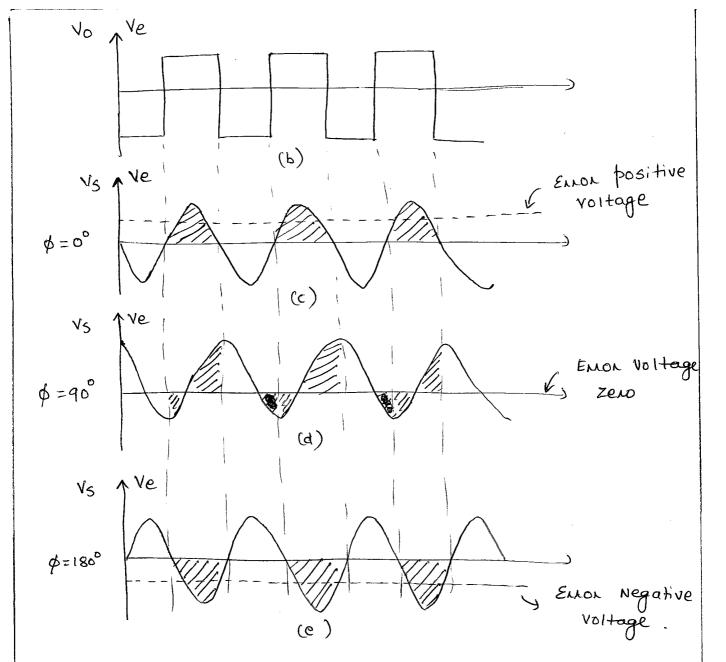

IC565 PLL – Block Schematic, Description of Individual Blocks, Applications.

# UNIT-1

| Integrated Cincuits and Operational Amplifier          |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|

| Definition of IC : The Integrated circuit (01) IC is a |  |  |  |  |  |

| miniature, low cost electronic circuit consisting of   |  |  |  |  |  |

| active and passive components that are inneparably     |  |  |  |  |  |

| joined together on a single crystal chip of silicon.   |  |  |  |  |  |

| Advantages of Ics:                                     |  |  |  |  |  |

| 1. Miniaturization and hence increased equipment       |  |  |  |  |  |

| density                                                |  |  |  |  |  |

| 2. cost reduction due to batch processing              |  |  |  |  |  |

| 3. Increased system neliability due to elimination     |  |  |  |  |  |

| of soldered joints                                     |  |  |  |  |  |

| 4. Improved functional performance                     |  |  |  |  |  |

| 5. Increased operating speeds                          |  |  |  |  |  |

| 6 Reduction in power consumption.                      |  |  |  |  |  |

| classification of IC's :                               |  |  |  |  |  |

| I Based on mode of operation:                          |  |  |  |  |  |

| a) Digital IC'S b) Linean IC'S                         |  |  |  |  |  |

| (a) <u>Digital IC's</u> ; Digital IC's are complete    |  |  |  |  |  |

| functioning logic networks that are equivalents        |  |  |  |  |  |

| of basic transistor logic circuits.                    |  |  |  |  |  |

| Ex: Gates, counters, multiplexens, demultiplexens,     |  |  |  |  |  |

| shift negistens.                                       |  |  |  |  |  |

Linean IC's: Linean IC'S are equivalents of discrete transiston networks, such as amplifiens, filtens, frequency multipliens and modulators that often require additional external components for satisfactory operation.

Ex: OP-AMPS

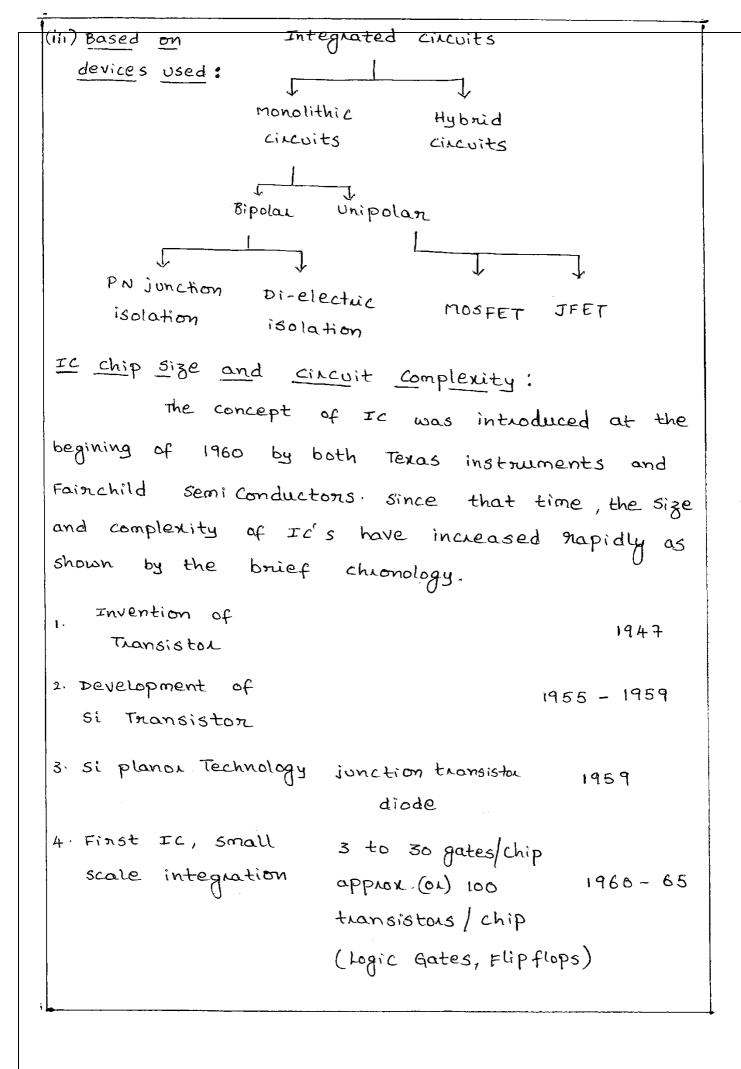

I Based on Fabrication

a) Monolithic Ic's b) Hybrid Ic's a) <u>Monolithic Ic's</u>: In monolithic Ic's all components (active and passive) are formed simultaneously by a diffusion process. Then a metallization process is used in interconnecting these component to form the desired circuit.

b) <u>Hybrid</u> <u>IC's</u>: In Hybrid IC's, passive component (Such as resistons and capacitons) and the interconnections between them are formed on an insulating substrate, the substrate is used as a chassis for the integrated components. Active components such as transistons and diodes as well as monolithic integrated circuits, are then connected to form a complete circuit.

Manufacturers Designations for integrated circuits Each manufacturer uses a specific x and assigns a specific type number to the Ic's it produces. That is, each manufacturer uses its own identifying initials followed by its own type number.

For example, the 741 type of internally compensated op-Amp was originally manufactured by Fairchild and is sold as the MA741, where MA Represents the identifying initials used by fair. Chaild. Initials used by some of the well known Manufacturers of Linear Ic's are as follows

Fainchild : MA, MAF

National SemiConductor : LM, LH, LF, TBA

Motorola : MC, MFC

Texas instruments : SN

RCA : CA, CD Signetics ; N/S, NE/SE, SU

BUAN BAOWN ; BB

Fairchild's original MA 741 is also manufactured by Various other manufacturers under their own designations, as follows. -

| National semiconductor                            | LM 741   |  |  |  |  |  |

|---------------------------------------------------|----------|--|--|--|--|--|

| Motorola                                          | MC1741   |  |  |  |  |  |

| RCA                                               | CA 3741  |  |  |  |  |  |

| Texas Instruments                                 | SN 52741 |  |  |  |  |  |

| signetics                                         | N5741.   |  |  |  |  |  |

| Temperature ranges of Ic's:                       |          |  |  |  |  |  |

| All Ic's manufactured fall in to one of the three |          |  |  |  |  |  |

| basic temperature grades.                         |          |  |  |  |  |  |

| 1. Military temperature stange -55°C to 125°C     |          |  |  |  |  |  |

| 2. Industrial temperature gange -20°C to +85°C    |          |  |  |  |  |  |

| 3. commercial temperature siange o'c to t70°C.    |          |  |  |  |  |  |

| Applications of IC                                |          |  |  |  |  |  |

| Ic's have become a vital part of modern           |          |  |  |  |  |  |

| electronic circuit design they are used in        |          |  |  |  |  |  |

| 1. Computer Industry                              |          |  |  |  |  |  |

| 2. Automobile Industry                            |          |  |  |  |  |  |

| 3. Home appliances                                |          |  |  |  |  |  |

| 4. communication                                  |          |  |  |  |  |  |

| 5. control systems                                |          |  |  |  |  |  |

| where they permit miniaturization and             |          |  |  |  |  |  |

| superior performance not possible with            |          |  |  |  |  |  |

| discuete Components.                              |          |  |  |  |  |  |

OPERATIONAL AMPLIFIER (OP-AMP) \* An Impontant Linean IC is operational Amplifien. \* the operational Amplifier is a multiterminal device which internally is quite complex. \* OP-AMP is a direct coupled high gain Amplifier \* op-Amp can be used to amplify both a.c and d.c signals. \* st is used to perform a Variety of mathemati--cal operations such as Addition, subtraction, log, Antilog, Differentiation, Integration etc. Hence the Due to its use in performing mathematical operations, it has been given a name 'operational Amplifien' \* Earlier op-Amps were designed by Using Vaccum tubes, Hence the op-Amps were bulky, power consuming and expensive. \* Between 1964 to 1968 the popular 741 integrated circuit op-Amp was introduced by Robert j-widlar \* the IC vension of OP-AMP Uses BJT's and FET'S which are fabricated along with the other supporting components on a single semi conductor chip. Advantages: Low cost, small size, vensatile, flexible

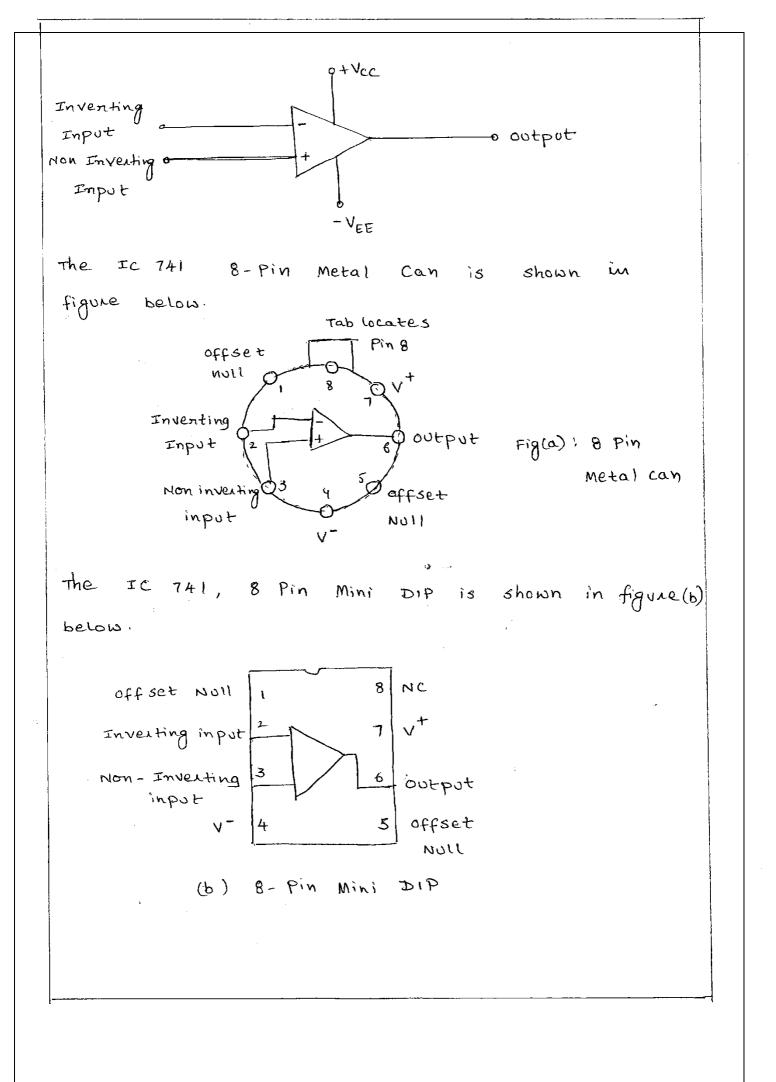

Applications : communications, computers, power and signal sources, process control, displays and measuring systems. op-Amp symbol and Terminals : op-Amp symbol: The circuit schematic of an op-Amp is a triangle as shown in figure below. two input terminals and one output has 9t terminal Inventing output input terminal. Non Inverting input packages : There are three popular packages available 1. The metal can (TO) package 2. The flat package (or) flat pack 3. The dual - in - Line package (DIP) OP-AMP Terminals: OP-Amps have five basic terminals, that is 1. Two input terminals 2. one output terminal 3. Two power supply terminals.

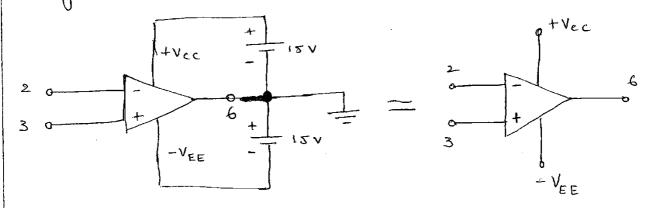

Powen Supply connections;

The  $\pm V_{CC}$  and  $-V_{EE}$  power Supply terminals are connected to two dc Voltage Sources. The  $\pm V_{CC}$  is connected to the positive terminal of one source and  $-V_{EE}$  is connected to the negative terminal of other source. where the two sources are 15V batteries each. These are typical Values, but in general, the power supply Voltage may Plange from about  $\pm 5V$  to  $\pm 22V$ . The common terminal of  $\pm V_{CC}$  and  $-V_{EE}$  is connected to a reference point or ground.

The Ideal operational Amplifier:

The schematic symbol of an op-Amp is shown in figure below. The - and + symbols at the input refer to inventing and non inverting input terminals Respectively. ie of  $V_1=0$ , output  $V_0$  is  $180^\circ$  out of phase with input signal  $V_2$ .

And when  $v_2 = 0$ . Output vo will be imphase with the input signal applied at VI.  $V_{2} \xrightarrow{\rightarrow i_{2}=0} V_{d} \xrightarrow{} V_{d}$ Fig(a): Ideal op\_Amp The op-Amp is said to be ideal if it has the following characteristics. 1. Infinite voltage gain AOL = 00 since gain is oo, the voitage between the inverting and non inverting terminals ie differential input voltage Vd = V1-V2 is essentially zero for finite output voltage Vo.  $A_{0L} = \frac{V_0}{V_A} = \infty \implies V_A = 0 = V_1 - V_2$ 2. Infinite input mesistance (R: = 00): Because of infinite input resistance the ideal op-Amp draws no current at both the input terminals i.e.  $i_1 = i_2 = 0$ . so that almost any signal source can drive it and there is no loading of the preceding stage.

6

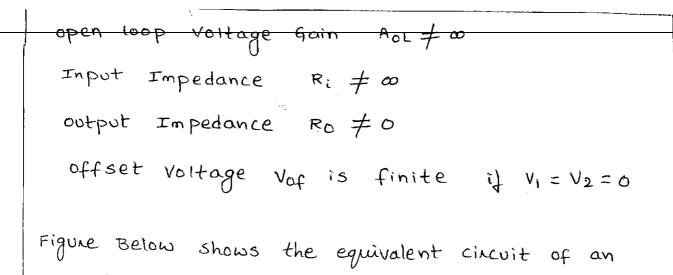

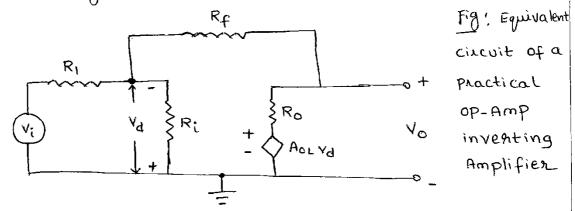

3. zero output Resistance (Ro=0) so the output can drive an infinite number of other sources. 4. Infinite Band width  $(BW = \infty)$ so that any frequency signal from o to a Hz can be amplified with out attenuation 5. offset vortage Vof = 0 ie when  $V_1 = V_2 = 0$ ,  $V_0 = 0$ 6. common mode Rejection Ratio (CMRR) = 00 7. slew nate  $(SR) = \infty$ the output voltage changes occur 50 simultaneously with input voltage changes. Practical OP-AMP [Equivalent circuit of OP-AMP]: The ideal op-Amp characteristics can never be realized in practice . There are practical op-Amps that can be made to approximate some of these characteristics. using a negative feedback amangement. the physical Amplifier is not a ideal one so the characteristics of practical op-Amp an

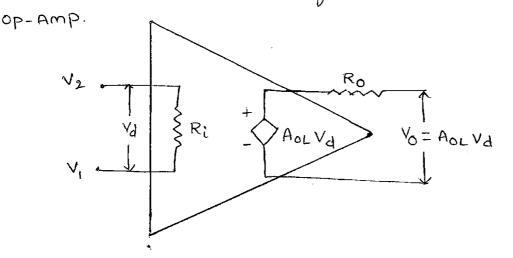

For the above circuit  $A_{0L} \neq \infty$ ,  $R_i \neq \infty$  and  $R_0 \neq 0$ . It can be seen that op-Amp voltage controlled voltage source and  $A_{0L}V_d$  is an equivalent the vinin voltage Source and  $R_0$  is the the vinin equivalent resistance looking back in to the output terminal of an op-Amp.

the equivalent circuit is useful in analyzing the basic operating principles of op-Amps. For the above circuit, the output Voltage is

Vo = AOL Vie

$V_0 = A_{0L} (V_1 - V_2)$

the equation shows that the op-Amp amplifies the difference between the two input voltages.

.

open loop operation of op-Amp: (op-Amp without feedback) The simplest way to use an op-Amp is in the open loop mode Val + Vo V2 V1 + Vo

Refer to the above figure, where signals V1 and V2 are applied at non investing and investing input terminals Respectively.

since the gain is infinite, the output Voltage No is either at its positive saturation voltage (+Vsat) or negative saturation Voltage.

$Sf \quad V_1 > V_2 \implies V_0 = + V_{sat} = + V_{cc}$

$V_1 < V_2 \implies V_0 = -V_{sat} \simeq -V_{cc}$

Here the output assumes one of the two possible output states, that is +Vsat at -Vsat and the amplifier acts as a switch only.

This has limited number of applications such as voitage comparator, zero Guming detector etc. open loop op-Amps are not used in linear For practical op-Amp (open loop) applications.

$V_2 = 0$   $V_0$

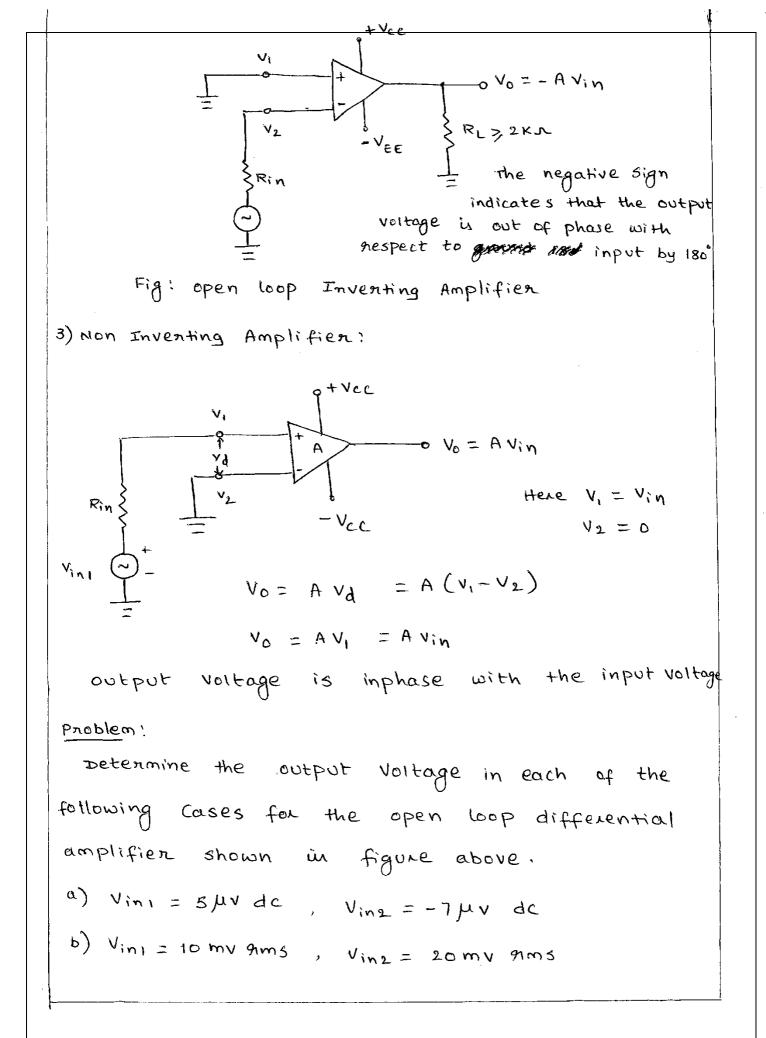

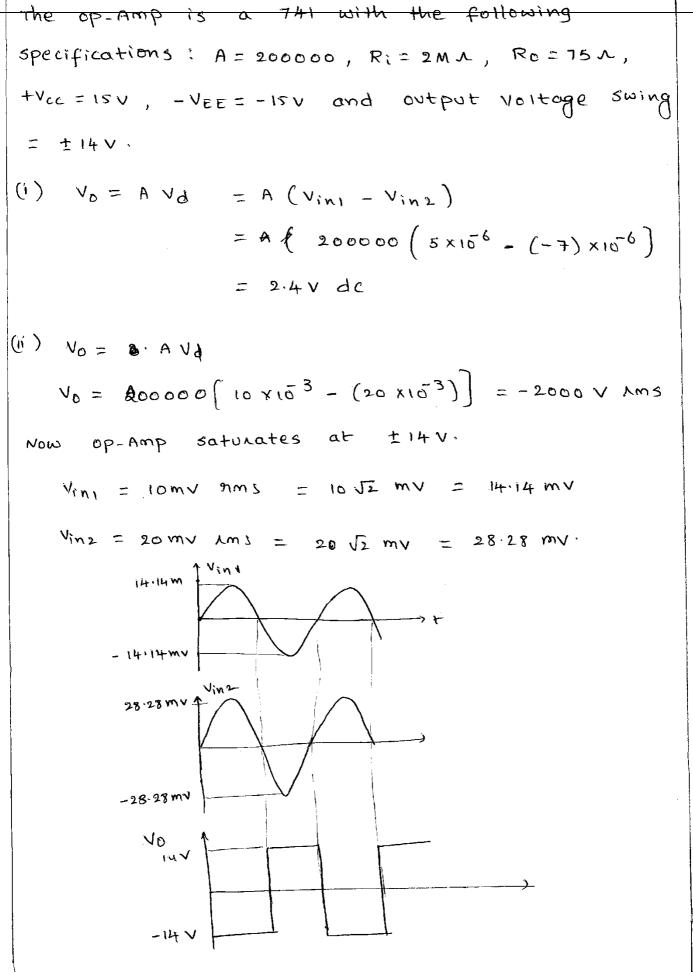

Assume AOL = 105  $V_0 = A_{0L}V_d = A_{0L}(V_1 - V_2)$ VO = AOL VI case 1:  $9f V_{1} = 1 \mu V \implies V_{0} = 10^{5} \times 10^{6} = 0.1 V$ case 2:  $v_0 = 100 \text{ V} = 100 \text{ V} = 100 \text{ V}$ To consider case (2): output voltage 100 V is not possible, because output voltage cannot be greater than supply voltage. so output is saturated 50 Vo = + Vsat ~ + Vcc similarly st V1=0  $\frac{case}{1} = \frac{1}{9} \frac{1}{1} \frac{1}{1}$  $\frac{\text{case 2}}{\text{sec 2}} \quad \text{sec 2} \quad \text{sec$ open loop op-Amp configurations: there are three open loop op-Amp configurations + Differential Amplifier 2. Inventing Amplifier 3. Non inventing Amplifier. 1. Differential Amplifier: Figure shows the open loop differential Amplifier in which input signals Vinjand Vinzare opplied to the positive and Negative input terminals.

Since the op-Amp amplifies the difference between

the two input signals, this configuration is called

the differential amplifier.

$$V_{1}$$

+ Vec

$V_{2}$  + Vec

$V_{2}$  + Vec

$V_{3}$  + Vec

$V_{4}$  + Vec

$V_{5}$  =  $V_{5}$  +  $V_{5}$  +  $V_{5}$  =  $V_{5}$  =  $V_{5}$  +  $V_{5}$  +  $V_{5}$  =  $V_{5}$  +  $V_{5}$  +  $V_{5}$  =  $V_{5}$  +  $V_{5}$

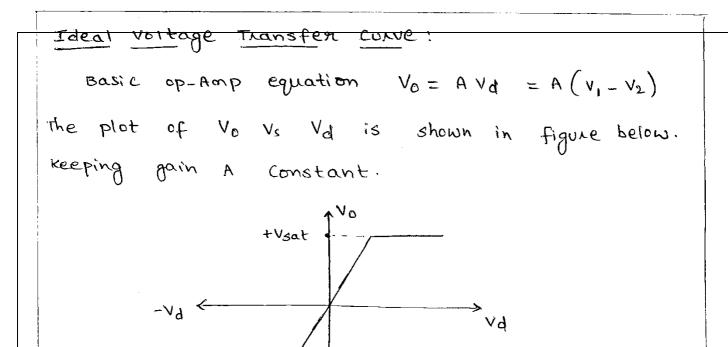

Here Fig! Ideal voltage transfer CURVE Here Ideal because output offset voltage is assumed to be zero.

-Vsat

From the graph we can say that the ouput Voltage is directly proportional to the input difference Voltage only until it Aeaches the saturation voltages and that thereafter output voltage Aemains constant. Feedback in Ideal OP-AMP: (Negative feedback)

The utility of an op-Amp can be greatly increased by providing Negative feed back. The output in this case is not driven in to saturation and the circuit behaves in a linear manner. There are two basic feed back connections used. In order to understand the operation of these circuits, we make two realistic simplying assumptions. If the current drawn by either of the input terminals (non inverting and inverting) is negligible 2. The differential input voltage Vd between noninverting and inverting input terminals is essentially Zero.

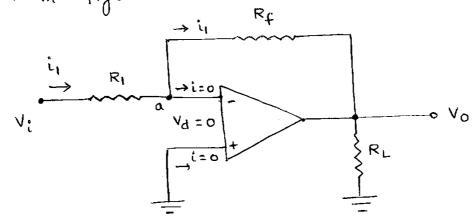

#### Inventing Amplifien:

The cincuit of Inventing Amplifier circuit is shown in figure below.

Fig: Inverting Amplifier

The output Voltage Vo is fedback to the inventing input terminal through the Rf-Ri network where Rf is the feedback resistor. Input signal Vi (ac on de) is applied to the inverting input terminal through Ri and non inverting input terminal of OP-Amp is grounded. Analysis

Analysis:

For simplicity, assume an ideal op-Amp. As Vd=0, node 'a' is at ground potential and the current if through  $R_1$  is  $i_1 = \frac{V_1}{R_1} \longrightarrow 0$

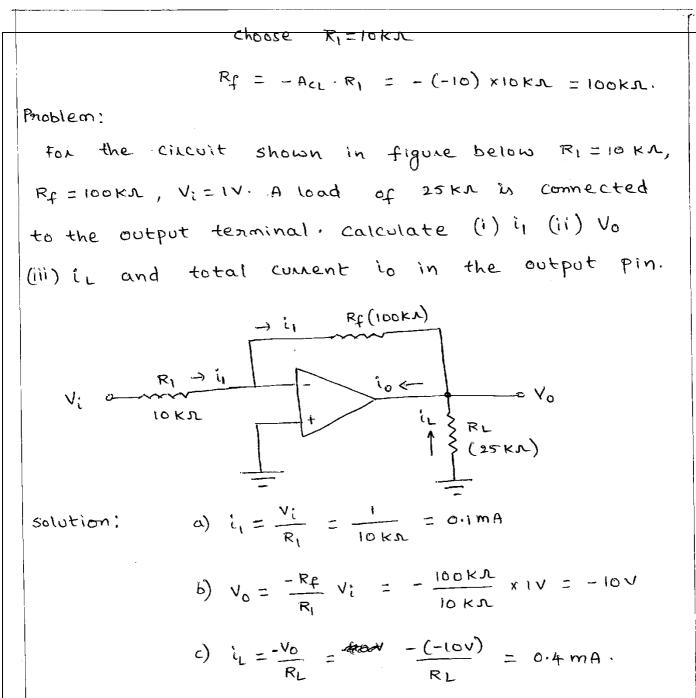

Also since op-Amp draws no current, all the current flowing through RI must flow through Rf. The output voitage From the circuit  $i_1 = \frac{V_i - V_a}{R_i} = \frac{V_i - o}{R_i} = \frac{V_i}{R_i} \longrightarrow (2)$  $i_1 = \frac{V_a - V_o}{R_f} = \frac{o - V_o}{R_f} = -\frac{V_o}{R_f} \longrightarrow 3$ ٤ = 3  $\frac{V_i}{R_i} = \frac{-V_0}{R_f} \implies A_{cL} = \frac{V_0}{V_i} = \frac{-R_f}{R_i},$ The negative sign indicates a phase shift of 180° between Vi and Vo. Also since inventing input terminal is at Virtual ground, the effective input impedance is R1. The value of Ri should be kept fairly large to avoid loading effect. Problem Design an Amplifier with a gain of -10 and input resistance equal to lokr. solution! since the gain of the amplifien is negative, an inventing amplifien has to be made. The gain of inventing amplifien is  $A_{CL} = \frac{-\kappa_f}{R_L}$  $-10 = \frac{-R_f}{R_i} \implies$

d) Total current  $i_0 = i_1 + i_L = 0.1 + 0.4$  $i_0 = 0.5 \text{ mA}$ .

In an inventing amplifier, for a tre input output will be -re, therefore the direction of to is as shown in figure above Practical Inventing Amplifien:

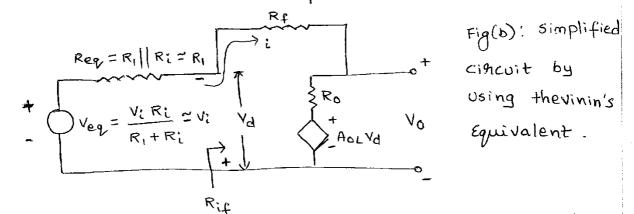

For a practical op-Amp the expression for the closed loop voltage gain should be calculated using the low frequency model of inverting Amplifien The equivalent circuit of a practical inverting amplifien is shown in figure below.

This cincuit can be simplified by replacing the signal source V: and Resistons R, and R: by the vinin's equivalent as shown in figure below, which is analysed to calculate the exact expression for closed loop gain Ach and input impedance Rif.

Fig: Simplified circuit by using the vinin's equivalent the input impedance  $R_i$  of an Op-Amp is usually much greater than  $R_i$ , so we may assume  $Veq \cong V_i$  and  $Req = R_i$ .

From the output loop in figure (b)

$$V_{0} = iR_{0} + A_{0L}V_{d} \longrightarrow 0$$

Also  $V_{d} + iR_{f} + V_{0} = 0 \longrightarrow (3)$

putting the value of  $V_{d}$  from  $e_{f}(3)$  to  $e_{f}(0)$  and

simplifying

$$V_{0} = iR_{0} + A_{0L} (-iR_{f} - V_{0})$$

$$V_{0} (i+A_{0L}) = i(R_{0} - A_{0L}R_{f}) \longrightarrow (3)$$

Also the KVL loop equation gives

$$V_{i} = i(R_{1}+R_{f}) + V_{0} \longrightarrow (4)$$

putting the value of i from  $e_{f}(3)$  in  $e_{f}(3)$

and solving for closed loop gain

$$A_{cL} = \frac{V_{0}}{V_{i}}$$

$$V_{i} = \frac{V_{0}(i+A_{0L})}{R_{0} - A_{0L}R_{f}} \quad (N_{i} = R_{i} + R_{f}) + V_{0}$$

$$V_{i} = \frac{V_{0}(i+A_{0L})}{R_{0} - A_{0L}R_{f}} \quad (N_{i} = R_{i} + R_{f}) + V_{0}$$

$$V_{i} = \frac{V_{0}(i+A_{0L})}{R_{0} - A_{0L}R_{f}} \quad (N_{i} + R_{f}) + V_{0} = N_{0} - V_{0}A_{0}R_{f}$$

$$V_{i} (R_{0} - A_{0L}R_{f}) = V_{0} (I + A_{0L}) (R_{1} + R_{f}) + V_{0} = N_{0} - V_{0}A_{0}R_{f}$$

$$V_{i} (R_{0} - A_{0L}R_{f}) = V_{0} (I + A_{0L}) (R_{1} + R_{f}) + V_{0} = N_{0} - V_{0}A_{0}R_{f}$$

$$V_{i} (R_{0} - A_{0L}R_{f}) = V_{0} (I + A_{0L}) (R_{1} + R_{f}) + V_{0} = N_{0} - V_{0}A_{0}R_{f}$$

$$V_{i} (R_{0} - A_{0L}R_{f}) = V_{0} R_{i} + V_{0}R_{0} - V_{0}A_{0}R_{f}$$

$$V_{i} (R_{0} - A_{0L}R_{f}) = V_{0}R_{i} + V_{0}R_{0} - V_{0}A_{0}R_{f}$$

$$V_{i} \left( R_{0} - A_{0L} R_{f} \right) = V_{0} \left( R_{0} + R_{f} + R_{1} \left( 1 + A_{0L} \right) \right)$$

$$A_{CL} = \frac{V_{0}}{V_{i}} = \frac{R_{0} - A_{0L} R_{f}}{R_{0} + R_{f} + R_{1} \left( 1 + A_{0L} \right)}$$

$$\left[ \begin{array}{c} \$f \quad A_{0L} >> 1 \\ A_{CL} = \frac{R_{0} - A_{0L} R_{f}}{R_{0} + R_{f} + A_{0L} R_{1}} \quad \text{and} \quad A_{0L} R_{1} >> R_{0} + R_{f} \\ A_{CL} = \frac{-R_{f}}{R_{1}} \\ \end{array} \right]$$

$$\frac{I_{R}Put}{R_{c} + R_{f}} \xrightarrow{Resistance} \frac{R_{i}f}{R_{i}} := F_{A}cm \quad fig(8)$$

$$\frac{R_{i}f}{R_{i}f} = \frac{V_{d}}{i}$$

$$\frac{V_{d} + i \left( R_{f} + R_{0} \right) + A_{0L} V_{d} = 0}{V_{d} \left( 1 + A_{0L} \right)} = - \left( R_{f} + R_{0} \right) i$$

$$\frac{R_{i}f}{I} = \frac{V_{d}}{i} = \frac{-\left( R_{f} + R_{0} \right)}{I + A_{0L}}$$

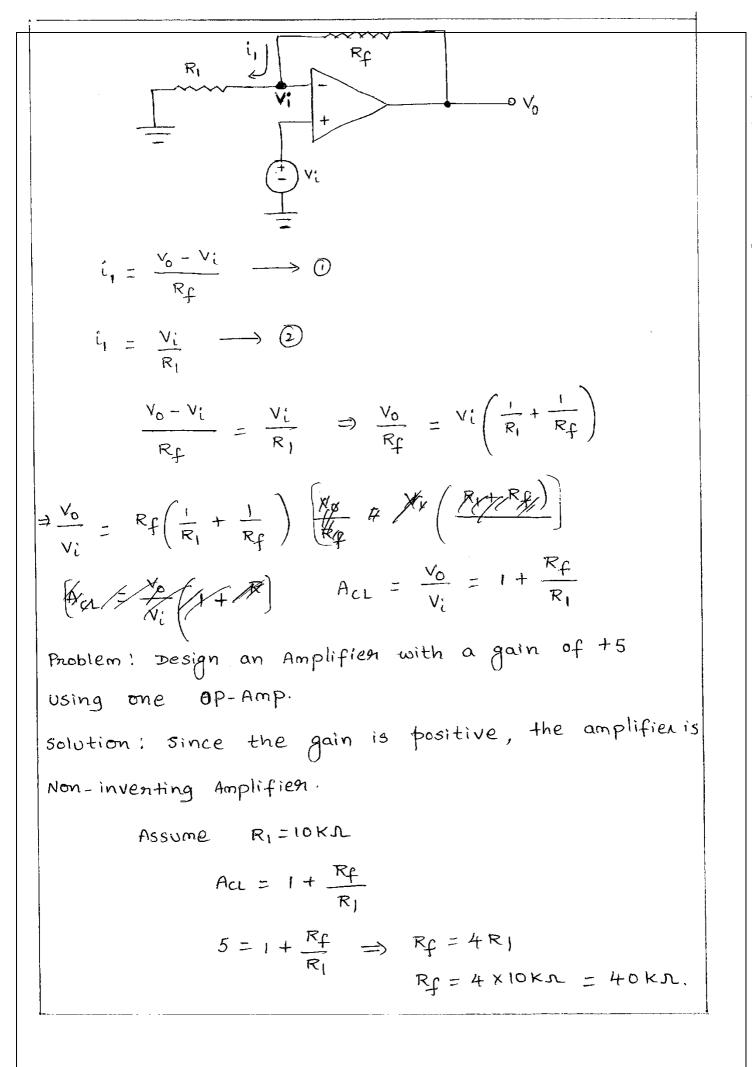

Non inventing Amplifien:

If a signal (ac or dc) is applied to the noninventing input terminal and feedback is given as shown in figure below.

The circuit amplifies with out inventing the input signal. Such a circuit is called non-inventing amplifier. It may be noted that it is also a negative feed-back system as feed back is being fed back to the inventing input terminal.

Problem: In the circuit shown in figure below let

$$R_{1}=5ka$$

,

$R_{f} = 20 \text{ k.r.}$  and  $V_{i} = 1 \text{ V. A}$  load gresistor of  $5 \text{ K.r.}$  is

connected at the output. calculate

(1)  $V_{0}$  (ii)  $A_{CL}$  (iii) the load cument  $i_{L}$  (iv) the output

connect is indicating problem direction of flow.

Solution:

(i)  $V_{0} = \left(1 + \frac{R_{f}}{R_{I}}\right) V_{i} = \left(1 + \frac{20 \text{ k.r.}}{5 \text{ k.r.}}\right) (iv) = 5v$

(ii)  $A_{CL} = \frac{V_{0}}{V_{i}} = \frac{5v}{iv} = 5$

(iii)  $A_{CL} = \frac{V_{0}}{V_{i}} = \frac{5v}{iv} = 5$

(iii)  $A_{CL} = \frac{V_{0}}{V_{i}} = \frac{5}{5 \text{ k.r.}} = 1 \text{ mA}$

(iv)  $i_{L} = \frac{V_{0}}{R_{L}} = \frac{5}{5 \text{ k.r.}} = 1 \text{ mA}$

(iv)  $i_{0} = i_{L} + i_{1} = 1 \text{ mA} + 0.2 \text{ mA} = 1.22 \text{ mA}$

the op-Amp output current is flows outwards from

the output junction.

practical Non-Inventing Amplifien:

The analysis of practical non-inventing Amplifier

can be performed by using the equivalent circuit shown

in figure bolow.

Rf

RI

(Vd+Vi)

Vd Ri

Vd Ri

Vd Ri

Vd Ri

Vd Vd

Fig: Equivalent circuit of Non inventing Amplifier using

Low frequency model.

writing kcl at the input Node

$$(V_0 - (V_d + V_i))Y_f = (V_d + V_i)Y_1 + V_d Y_i$$

$Y_4 V_0 = V_d (Y_1 + Y_1 + Y_4) + V_i (Y_1 + Y_4) \rightarrow 0$

writing kcl at the output node

$(V_0 + (V_d + V_i))Y_f = (V_0 - A_{0L} V_d)Y_0$

$V_0 (Y_f + Y_0) = V_d (A_{0L} Y_0 + Y_f) + Y_f V_i \rightarrow 0$

From Eq. 0.  $V_d = \frac{Y_f V_0 - (Y_1 + Y_f) V_i}{Y_1 + Y_4} \rightarrow 3$

Substitute Eq. 3 in Eq. 0, After simplifying

$$A_{cL} = \frac{V_{0}}{V_{i}} = \frac{A_{0L} Y_{0} (Y_{1} + Y_{f}) - Y_{f} Y_{L}}{(A_{0L} - 1) Y_{0} Y_{f} - (Y_{1} + Y_{i}) (Y_{0} + Y_{f})}$$

This is the nequined closed loop gain of practical NOM inventing Amplifier.

$$\left[F_{0A} \text{ Ideal Amplifier.}, A_{0L} \rightarrow \emptyset, \text{ so using in } \mathcal{E}_{q}(\widehat{\Phi}), \\ \text{we get} \\ A_{cL} = \frac{A_{0a} Y_{0} (Y_{1} + Y_{f}) - \frac{Y_{f} Y_{i}}{A_{0L}} - \frac{(Y_{1} + Y_{i}) (Y_{0} + Y_{f})}{A_{0L}} \right|_{A_{0L} \rightarrow \emptyset} \\ A_{cL} = \frac{Y_{0} (Y_{1} + Y_{f})}{Y_{0} Y_{f}} = 1 + \frac{Y_{1}}{Y_{f}} \simeq 1 + \frac{R_{f}}{R_{1}} \\ \text{Vintual Ground:} \\ \text{The differential input voltage V_{d} between the non inventing and inventing tenminals is essentially zero. This is obvious because even if output voltage is few volts, due to large open loop gain of op-Amp, the difference voltage V_{d} at the input terminals is almost zero. \\ \underline{St} \text{ of output Voltage is lov and the A_{0L} is 10^{+} then } \\ V_{0} = V_{d} A_{0L} \\ \end{array}$$

$$V_d = \frac{V_0}{A_{0L}} = \frac{10}{104} = 1 MV$$

Hence  $V_d$  is Veny Small. As  $A_{OL} \rightarrow \infty$ , the differential voltage  $V_d \rightarrow 0$ , and assumed to be zero for analysing the circuits.  $V_d = \frac{V_0}{A_{OL}} \Rightarrow V_1 - V_2 = \frac{V_0}{A_{OL}} = \frac{V_0}{\infty} = 0$   $V_1 = V_2$   $V_1 = V_2$   $V_1 = V_2$   $V_1 \rightarrow I$   $V_1 = V_2$   $V_1 \rightarrow I$   $V_1 = V_2$   $V_2 \rightarrow I$   $V_1 = V_2$   $V_2 \rightarrow I$   $V_1 = V_2$   $V_2 = V_2$   $V_1 = V_2$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_1 = V_2$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_1 = V_2$   $V_2 \rightarrow I$   $V_3 \rightarrow I$   $V_1 \rightarrow I$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_3 \rightarrow I$   $V_1 \rightarrow I$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_3 \rightarrow I$   $V_3 \rightarrow I$   $V_1 \rightarrow I$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_3 \rightarrow I$   $V_1 \rightarrow I$   $V_2 \rightarrow I$   $V_2 \rightarrow I$   $V_3 \rightarrow I$   $V_3 \rightarrow I$   $V_3 \rightarrow I$   $V_3 \rightarrow I$   $V_1 \rightarrow I$   $V_2 \rightarrow I$   $V_3 \rightarrow I$

Thus we can say that under linear Mange of operation there is virtually short cincuit between the two input terminals, in the sense that their Voltages are same. No correct flows from input terminals to the ground.

The above figure shows that the concept of Vintual ground. The thick line indicates the Vintual short between the input terminals.

Now if the non-inventing terminal is grounded by the concept of Vintual short, the inventing terminal is also at ground potential, though there is no physical connection between the inverting terminal and the ground. This is the principle of Vintual ground.

Voltage Follower:

In the Non-inverting amplifien if Rf=0 and

R1=00, we get the modified circuit shown in figure

below

$$v_i + \frac{1}{2}$$

Here  $V_b = V_i$  and  $V_a = V_b$

$\therefore V_a = V_i$

Now  $V_0 = V_a$  and  $V_0 = V_i$

That is the output voltage is equal to imply voltage

both in magnitude and phase. In other words we

can say that the output voltage follows the input

Voltage exactly. Hence the circuit is called a

Voltage Follower'.

gt is also called buffer Amplifier. Unity gain

amplifier and isolation Amplifier.

Advantages:

I- Input impedance in Very high (ic Mr), low

potput impedance. therefore it draws neglégible

current from the source. Thus a voltage fellower

may be used as buffer for impedance matching that is, to connect a high impedance source to a low impedance load.

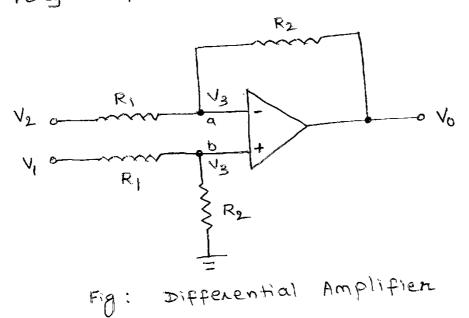

2. 9t has large band width Differential Amplifien:

A circuit that Amplifies the difference between two signals is called a difference or differential amplifier. This type of the amplifier is very useful in instrumentation circuits.

$\frac{V_2 - V_3}{R_1} = \frac{V_3 - V_0}{R_2}$

and

$$\begin{pmatrix} \frac{1}{R_1} + \frac{1}{R_2} \end{pmatrix} V_3 = \frac{V_1}{R_1}$$

$\frac{V_1 - V_3}{P_1 - V_3} = \frac{V_3}{R_2}$

After simplifying

$$V_0 = \frac{R_2}{R_1} \left( V_1 - V_2 \right)$$

Such a circuit is Very useful in detecting Very small differences in signals. Since the gain  $\frac{R_2}{R_1}$  can be chosen to be Very large For example of  $R_2 = 100 R_1$ , then a small difference  $N_1 - N_2$  is amplified 100 times.

Difference mode and common mode Gains. Output of a differential amplifier

$$V_{0} = \frac{R_{2}}{R_{1}} \left( V_{1} - V_{2} \right) \longrightarrow \textcircled{}$$

If  $V_1 = V_2$  then  $V_0 = 0$ . That is the signal common to both inputs gets cancelled and produces no output voltage. This is true for an ideal op-Amp, however a practical op-Amp exhibits some small response to the common mode component of the input voltages too.

For example, the output  $V_0$  will have different Value for cases (i) with  $V_1 = 100 \mu V$  and  $V_2 = 50 \mu V$ (ii) with  $V_1 = 1000 \mu V$  and  $V_2 = 950 \mu V$  even though the difference signal  $V_1 - V_2 = 50 \,\mu V$  in both the cases.

the output voltage depends not only upon the difference signal Vd at the input, but is also affected by the average voltage of the input signals, called the common-mode signal VcM defined as

$$V_{\rm CM} = \frac{V_1 + V_2}{2}$$

For differential amplifier, though the circuit is symmetric, but because of the mismatch the gain at the output with Respect to the positive terminal is slightly different in Magnitude to that of the negative terminal so even with the same voltage applied to both inputs, the output is not Zero. The output therefore must be expressed as

$V_0 = A_1 V_1 + A_2 V_2 \longrightarrow (2)$

where  $V_1 = Voltage$  multiplication from input 1 to the output with input 2 grounded  $V_2 = Voltage$  Multiplication from input 2 to the output with input 1 grounded. Since  $V_{cm} = \frac{V_1 + V_2}{2}$  and  $V_d = (V_1 - V_2)$  $V_1 = V_{cm} + \frac{1}{2}V_d \longrightarrow 3$  $V_2 = V_{cm} - \frac{1}{2}V_d \longrightarrow 4$  Substitute the value of  $V_1$  and  $V_2$  in eq. (2), we get  $V_0 = A_{DM} V_d + A_{LM} V_{CM} \longrightarrow (4)$ where  $A_{DM} = \frac{1}{2} (A_1 - A_2)$

$A_{cm} = A_1 + A_2$

The voltage gain for the difference signal is ADM and that for the common mode signal is ACM Common mode Rejection Ratio:

the relative sensitivity of an OP-Amp to a difference signal as compared to a common mode signal is called common mode Rejection Ratio (CMRR) and gives the figure of merit (P) for the differential amplifier. So, CMRR is given by

$$P = \left| \frac{A_{DM}}{A_{cM}} \right|$$

and is usually expressed in decibels (dB) For example, the MA741 Op-Amp has a minimum CMRR of TO dB.

we should have  $A_{JM}$  large, Acm should be zero ideally. so, higher the value of CMRR, better is the op-Amp.

Problem:

Determine the output of a differential amplifier

for the input voltages of 300 µv and 240 µv. The

differential gain of the amplifier is 5000 and the

value of CMRR is (j) 100 (ii) 10<sup>5</sup>.

Solution:

CARR = 100, V<sub>1</sub> = 300 µv, V<sub>2</sub> = 240 µv

V<sub>d</sub> = V<sub>1</sub> - V<sub>2</sub> = 300 µv - 240 µv = 60 µv

V<sub>d</sub> = V<sub>1</sub> - V<sub>2</sub> =

$$300 µv - 240 µv = 60 µv$$

V<sub>cm</sub> =  $\frac{V_1 + V_2}{2}$  =  $\frac{300 µv + 240 µv}{2}$  = 270 µv

Abm = 5000

CMRR =  $\frac{A_{DM}}{A_{CM}} \Rightarrow A_{CM} = \frac{A_{DM}}{CMRR} = \frac{5000}{100}$

$\Rightarrow A_{CM} = 50$

V<sub>0</sub> = A<sub>DM</sub> Vd + Acm Vem

V<sub>0</sub> =  $(5000 \times 60 µv) + (50 \times 210 µv)$

V<sub>0</sub> =  $313 \cdot 5mv$ .

Case 2 : CMRR =  $10^5$ , V<sub>1</sub> =  $300 µv$ , V<sub>2</sub> =  $240 µv$

CMRR =  $\frac{A_{DM}}{A_{CM}} \Rightarrow A_{CM} = \frac{A_{DM}}{CMRR} = \frac{5000}{10^5} = 10^5$

However with Rcomp in the used, is given by  $V_{oT} = \left(1 + \frac{R_f}{R_I}\right) V_{ios} + R_f I_B V_{oT} = \left(1 + \frac{R_f}{R_I}\right) V_{ios} + R_f I_{os}$ Many op-Amps provide offset Compensation pins to nullify the off set voltage. Figure below gives the connections for the 741 OP-Amp. The manufacturens recomment that a loke potentiometer potentioneter be placed across offset null pins 1 and 5 and the wiper be connected to the negative supply pint. The position of the wiper is adjusted to nullify the output offset voitage. R2 RI ٧<sub>0</sub> Thermal Drift! Bias connent, offset connent and offset voltage change with temperature. A circuit carefully nulled at 25° c may not remain so when the temperature rises to 35°c. This is called drift. offset convent drift is expressed in nA/oc and offset voitage drift in mv/°c. These indicate the change in offset for each degree celcius change in temperature.

or negative with respect to ground. Therefore the Max offset voltage at the output of an inverting and hon inverting amplifier without any compensating technique

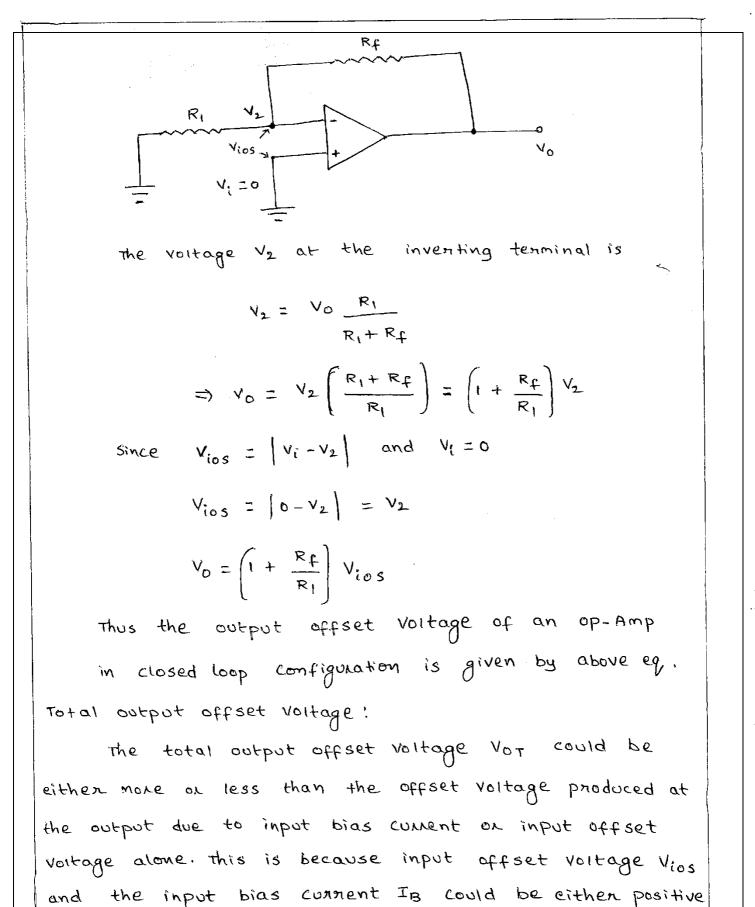

Input offset Voltage:

Inspite of the use of the above compensating techniques, it is found that the output voltage may still not be zero with zero input voltage. This is due to unavoidable imbalances inside the Op-Amp and a small voltage is to be applied of the input terminals to make output voltage zero. This voltage is called input offset voltage Vios. This is the voltage required to be applied at the input for making output voltage to zero volts as shown in figure below.

Fig(a): op-Amp showing input offset voltage.

Figure shows the non-inventing and Inventing Amplific ckts  $R_{i}$   $r_{i}$   $V_{i}$   $V_{i}$   $V_{i}$   $R_{i}$   $V_{i}$   $V_{i}$  $V_{i$

Fig(b): Non Inventing Amplifier Fig(c) ! Inventing Amplifier 9f V: is set to zero, the above circuits become the same a shown in figure below.

To obtain high input Resistance R, must be kept

lange. With RI lange, the feedback Resiston Rf must

also be high so as to obtain Reasonable gain.

The T-feedback network is a good solution. This

Will allow lange feedback Resistance while keeping

the Resistance to ground (seen by the inventing ilp)

low as shown in the dotted lines.

The T-network provides a feedback Signal as if the

network were a Single feedback Resiston

By T to TT Convention

$$R_f = \frac{Rt^2 + 2RtRs}{R_5}$$

.

To design a T-network, first fick

$R_t << R_f$  then Calculate  $R_f = \frac{Rt^2}{R_f - 2Rt}$ .

$R_f = \frac{Rt}{R_f}$  and  $R_f = \frac{Rt}{R_f} + \frac{Rt}{R_f}$ .

Fig: Inventing Amplifien with T-feedback Network

kci at node a' gives

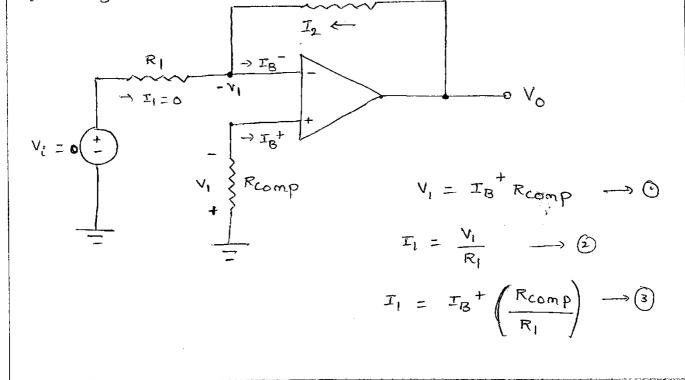

$$I_{B}^{-} = I_{1} + I_{2} \implies I_{2} = I_{B}^{-} - I_{1}$$

$$I_{2} = I_{B}^{-} - \left(I_{B}^{+} \frac{R_{comp}}{R_{1}}\right) \rightarrow (0)$$

Again

$$I_{2} = \frac{V_{0} + V_{q}}{R_{f}} \implies V_{0} = I_{2}R_{f} - V_{1}$$

$$V_{0} = I_{2}R_{f} - I_{B}^{+} (R_{comp})$$

$$\Rightarrow V_{0} = \mathbf{E} \left(I_{B}^{-} - \frac{I_{B}^{+} R_{comp}}{R_{1}}\right)R_{f} - I_{B}^{+} R_{comp}$$

$$V_{0} = \left(I_{B}^{-}\right) - \left(I_{B}^{+} \left(\frac{R_{comp}}{R_{1}} + R_{comp}\right)\right)\right)$$

$$V_{0} = I_{B}^{-}R_{f} - I_{B}^{+} R_{comp} \left(1 + \frac{R_{f}}{R_{1}}\right)$$

$$V_{0} = I_{B}^{-}R_{f} - I_{B}^{+} \frac{R_{f}R_{1}}{R_{f}+R_{1}} \left(\frac{R_{f}+R_{1}}{R_{1}}\right)$$

$$V_{0} = R_{f} \left(I_{B}^{-} - I_{B}^{+}\right)$$

Input offset Cunnent :

Bias concent compensation will WOAK if both bias concents  $I_B^+$  and  $I_B^-$  are equal. Since the input transistors cannot be made identical, there will always be some small difference between  $T_B^+$  and  $T_B^-$ . The difference is called the offset cornent Ios and Can be written as

$$|I_{OS}| = I_B^+ - I_B^-$$

The absolute value sign indicates that there is no way to predict which of the bias currents will be larger.

OFFSET CULLENT IOS FOR BJT OP-AMP is 200 hA FET OP-AMP is 10 PA.

Even with bias coment compensation, offset coment will produce an output voltage when the input voltage V: is zero. Rf

Ket at mode a For compensation ve should be zero for  $V_i = 0$ , that is from  $\mathcal{E}_{q}$  ()  $V_2 = V_1$ so that  $I_2 = \frac{V_1}{R_f}$ ket at node a gives  $I_B = I_2 + I_1 = \frac{V_1}{R_f} + \frac{V_1}{R_1}$ Assuming  $I_B = I_B^+$   $V_1 \left(\frac{1}{R_f} + \frac{1}{R_1}\right) = I_B^+$ From  $\mathcal{E}_{q}$  (2)  $V_1 \left(\frac{1}{R_f} + \frac{1}{R_1}\right) = \frac{V_1}{R_{comp}}$  $=) \frac{1}{R_{comp}} = \frac{1}{R_f} + \frac{1}{R_1}$

$\Rightarrow$  Rcomp = R<sub>1</sub>||Rf

That is to compensate for bias currents, the corresponding resistor  $\mathcal{R}_{comp}$  should be equal to the parallel combination of resistors tied to the inverting input terminal.

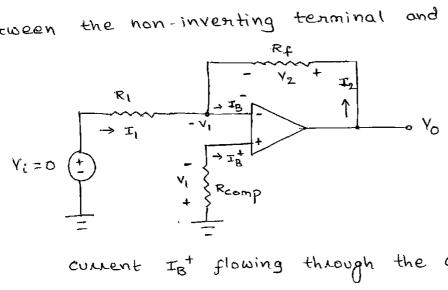

The Effect of input bias: current in a noninventing amplifier can also be compensated by placing a compensating nesistor,  $R_{comp}$ in Series with the input signal V: as  $R_{I}$ there  $R_{comp} = R_{I} || R_{f}$ . Here  $R_{comp} = R_{I} || R_{f}$ . For example, For a 741 op-Amp, with a  $Rf = IM\Lambda$   $V_0 = I_B Rf = 500 nA \times IM\Lambda = 500 mV$ with ZERO input, because of bias cunnents, the output is driven to soomv This Effect can be compensated for as shown in fig(c) where a compensation Aesiston Rcomp has been added between the non-inverting terminal and ground. Rf

CURRENT IB<sup>+</sup> flowing through the compensating Resistor R<sub>comp</sub> develops a voltage V, across it. Then by KVL we get

$$V_0 = V_2 - V_1 \longrightarrow (1)$$

By selecting proper value of Rcomp, V2 can be cancelled with V1 and the output V0 will be zero. The value of Rcomp is derived as

$$V_{1} = I_{B}^{+} R_{comp}$$

$$I_{B}^{+} = \frac{V_{1}}{R_{comp}} \longrightarrow 2$$

Now  $V_{a} = -V_{1} \implies I_{1} = \frac{V_{0}(-V_{1})}{R_{1}} = \frac{0+V_{1}}{R_{1}} = \frac{V_{1}}{R_{1}}$

Also  $I_{2} = \frac{V_{2}}{R_{f}}$

Even though both the transistons are identical,

$$T_B$$

and  $T_B^+$  are not equal due to internal imbalances

between the two inputs.

Manufacturens specify input bias current  $T_B$  as the

average value of the base currents entening in to the

tenminals of an OP-Amp.

so  $T_B = \frac{T_B^+ + T_B^-}{2}$

For  $741 \times opAmp \rightarrow T_B = 500 \text{ A}$  ( $T_B^+ = T_B^- = 500 \text{ A}$ )

For FET OP-Amp  $\rightarrow T_B = 500 \text{ A}$ .

consider the basic inventing Amplifier

$V_1 \rightarrow T_{1=0}$   $V_2$   $V_1 \rightarrow T_B^-$

Fig (b): Inventing Amplifier with bias cuarents

gf the input voltage  $V_1 = 0$ ,  $V_0$  should also be zero

$T_2 = \frac{V_0 - V_2}{T_1 = T_B}$

$T_2 = \frac{V_0 - V_2}{R_F} = T_B^-$

$V_0 - 0 = T_B^- R_F = V_0 = T_B^- R_F$

## Openational Amplifier characteristics

De Chanactenistics: An ideal op-Amp draws no connent from the source and its nesponse is also independent of tempenature. However a real op-Amp doesn't work this way. corrent is taken from the source in to the op-Amp inputs. Also the two inputs nespond differently to connent and voltage due to mismatch in transistons. A neal op-Amp also shifts its operation with tempenature. These non-ideal de chanactenistics that add ennon components to the de output voltage are

- 1) Input Bias CURRENT

- 2) Input offset Cunnent

- 3) Input offset Voltage

- 4) Thermal Drift.

1) Input Bias current:

practically input terminals conduct a small value of dc current to bias the input transistors. The base currents entening in to the inventing and non inventing terminals are shown as  $I_B^-$  and  $I_B^+$  grespectively. (Fig(a))  $\xrightarrow{\rightarrow I_B^+}$  Fig: Input Bias Currents

there are very few circuit techniques that can be used

to minimize the effect of drift. Caneful printed Circuit

board layout must be used to keep op-Amps away from

Source of heat. Forced air cooling may be used to

stabilize the ambient temperature.

problem:

a) For the non-inverting amplifien of

$$R_1 = 1KR$$

and

$R_f = 10KR$ . Calculate the maximum output offset voltage

due to Vies and IB. the op-Amp is LMBOT with

$V_{10S} = 10MV$  and IB = 300NA, Ios = 50NA.

b) calculate the value of Rcomp needed to beduce the

effect of IR

comp as calculated in (b) is connected in the circuit

solution:

a)  $V_{0T} = \left(1 + \frac{R_f}{R_1}\right) V_{10S} + R_f IB$

$V_{0T} = \left(1 + \frac{R_f}{R_1}\right) (0 mv) + (10KR)(300NR) = 113 mV$

b) the value of Rcomp Needed is

$R_{comp} = 1KR \left(10 KR = 990R$

e) with Rcomp in the circuit

$V_{0T} = \left(1 + \frac{R_f}{R_1}\right) V_{10S} + R_f IS = 110 mV + 0.5 mV$

$V_{0T} = (1 + \frac{R_f}{R_1}) V_{10S} + R_f IS = 110 mV + 0.5 mV$

$V_{0T} = (1 + \frac{R_f}{R_1}) V_{10S} + R_f IS = 110 mV + 0.5 mV$

problem ! A non inventing Amplifier with a gain of 100 15 nulled at 25°c: what will happen to the output voltage if the temperature Rises to 50°C for an offset voltage drift of oilsmu/°c? solution : Input offset voltage due to temperature nise Vios = 0.15 mV/°c X (50°C - 25°C) = 3.75 mV. since this is an input change, the output voltage will change by Vo = Vios X ACL Vo = 3.75 mV × 100 = 375 mV.

te chanactenistics:

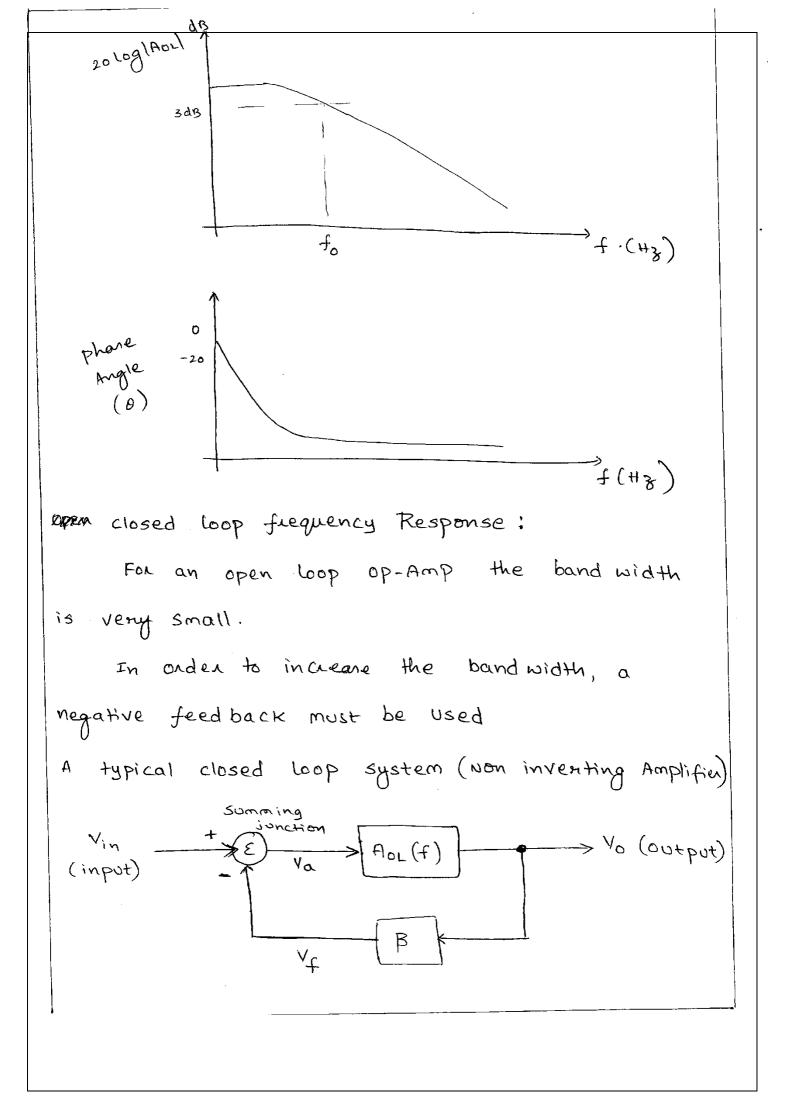

1. Frequency Response:

Ideally an OP-AMP should have an infinite bandwidth. The practical op-Amp gain, however decreases at higher frequencies, because of the capacitive component in the equivalent circuit of the OP-AMP.

Two major sources are responsible for capacitive effects

- 1. physical charactenistics of semi conductor devices; opamps are composed of BJT's and FET's which contain junction capacitons. As frequency increases, the neactance of these capacitors decrease

- 2. The Internal construction of the op-Amp is a second Source of capacitive effects. In op-Amps a number of transistors as well as nesistors and some times a capaciton are integrated on the same material, called a substrate. Infact, the substrate acts as an insulator and helps to separate these components. The various components are connected by conducting paths, and the paths are separated by insulators. However, whenever two conducting paths are separated by an insulator, it acts as a capacitor. This means that because of its construction the op-Amp may contain a number of such stray capacitors.

The cumulative effect of these capacitors due to the chanactenistics of semi conducton devices and the internal construction of the op-Amp causes the gain to decrease as the frequency increases. For an op-Amp with only one break frequency, we will represent all the capacitive effects by a single capaciton as shown in figure below.  $\vee_1$ <u>~</u>√₀ ξr: ٧d X ν, Fig: High frequency model of an op-Amp with Single break frequency. the gain on a function of frequency can be obtained as  $V_0 = \frac{-j x_c}{R_0 - j x_c} A V d$  $\frac{1}{12\pi fc} = \frac{1}{12\pi fc} = AVd$   $R_0 + \frac{1}{12\pi fc}$ Vo =  $V_0 = \frac{A V_d}{1 + j 2 \pi F R_0 C}$

Hence the open loop valtage gain is

$$A_{OL}(f) = \frac{N_{O}}{V_{d}}$$

$$A_{OL}(f) = \frac{A}{1+j 2\pi f R_{O} C}$$

Let  $P = f_{O} = \frac{i}{2\pi R_{O} C}$ , then

$$A_{OL}(f) = -\frac{A}{1+j \left(\frac{f}{f_{O}}\right)}$$

cohere  $A_{OL}(f) = Open loop voltage gain as a function of

frequency

$$A = Gain of the op-Amp at 0 Hz (dc)$$

$$f = Openating frequency

$$f_{O} = bneak frequency of the op-Amp.$$

Now the bneak frequency fo depends on the Value of

$$C \text{ and on output Aesistance Ro. Therefore fo}$$

is fixed for a given op-Amp.

$$IA_{OL}(f) = -tan^{-1}\left(\frac{f}{f_{O}}\right)$$

The open loop gain  $A_{OL}(f) dz$  is approximately

(constant from 0 Hz to the break frequency fo.$$$

$$A_{oL}(f) = \frac{V_{o}}{V_{a}} \quad \text{and} \quad B = \frac{V_{f}}{V_{o}}$$

$$V_{a} = V_{in} - V_{f} \quad \Longrightarrow \quad V_{in} = V_{a} + V_{f}$$

$$A_{cL}(f) = \frac{V_{o}}{V_{in}} = \frac{V_{o}}{V_{a} + V_{f}}$$

$$A_{cL}(f) = \frac{V_{o}/V_{o}}{V_{o}} \implies \frac{1}{V_{o}} + \frac{V_{f}}{V_{o}} \qquad \Longrightarrow \quad \frac{1}{V_{o}(f)} + B$$

$$A_{cL}(f) = \frac{A_{oL}(f)}{I + A_{oL}(f)} = \frac{A_{oL}(f)}{I + A_{oL}(f)} = \frac{V_{o}}{I + A_{oL}(f)}$$

system stability may be determined as follows. <u>method 1</u>: Determine the phane Angle when the Magnitude of AoL(f)B is OdB or 1. If the phase angle is > 180°, the system is stable. However for some systems the Magnitude may hever be odB. in that Case method 2 must be used to determine the system stability.

Method 2: Determine the Magnitude of Aol(f) B when the phase angle is -180°. If the Magnitude is negative decibels, then the system is stable. However some times the phase angle of a system may never Reach -180°, under such conditions, Method 1 must be used to determine the system stability.

slew Rate:

slew Rate is defined as the maximum nate of change of output voltage with nespect to time. a slew Rate is specified in Units of  $V/\mu s$ .

The general pumpose op-Amps such as 741 have a maximum slew rate of  $0.5 v/\mu s$ , which means that the output voltage can change at a maximum of 0.5 v in 1  $\mu s$ .

causes for slew Rate :

the slew Rate is detenorined by a number of factors such as the amplifien gain, compensating capacitors and the change in polarity of output voltage It is also a function of temperature and the slew Rate generally reduces due to rise in temperature.

The capacitor within on outside the op-Amp is nequired to prevent oscillation and this capacitor nestricts the nesponse of op-Amp to a rapidly changing input signal. The nate at which the voltage across the capacitor Vc increases is given by

$$\frac{dv_c}{dt} = \frac{T}{c}$$

where I is the connert furnished by the internal circuit. This means that the op-Amp Must have either a higher cornert or a small compensation capacitor.

For example To 741 can provide 15MA of Maximum

connect to its internal 30PF capacitor. that is

slew Rate =

$$\frac{dV_c}{dt}\Big|_{max} = \frac{T_{max}}{c} = \frac{15\mu A}{30PF} = 0.5 V/\mu s$$

Slew Rate Equation:

since the slew Rate is generally listed for a

onity gain let US consider the Voltage follower

shown in figure below.

Let us assume that the input is a large amplitude

and high frequency sine wave. The Equation for

the sine wave. Is

$V_{in} = V_{p} \sin \omega t$

$V_{0} = V_{p} \sin \omega t$

The state of change of the output is

$\frac{dV_{0}}{dt} = V_{p} w Cos \omega t$

and the maximum state of change of output

occurs when Cos = 1 that is

Slew Rate = 2TTFVp

slew Rate =

$$\frac{2\pi f V p}{10^6} V/\mu s$$

. 0

the maximum frequency fmax at which an undistanted output voltage with a peak value Vp Can be obtained is determined by

$$f_{max} = \frac{Slew Rate \times 10^6}{2 \text{ Tr Vp}}$$

The maximum peak sinusoidal output Voltage  $(V_P)_{max}$ that can be obtained at a frequency of f is given by  $(V_P)_{max} = \frac{Slew Rate \times 10^6}{2 \text{ Tr} f}$

problem: The op-Amp 741 Connected as a Unity gain inventing amplifier is applied with a input change of IOV. Determine the time taken for the output to change by IOV.

solution: FOL OP-AMP slew Rate = 0.5 / V/HS

$$Time = \frac{10N}{0.5V/\mu s} = 20\mu s.$$

problem: The slew Rate for 741 is 0.5 V/us what is the maximum undistorted sine wave that can be obtained for 12V peak.

OP-AMP Internal CILCUIT of four cascaded op-Amps usually consists blocks the block diagram of IC op-Amp is shown in figure below. Non inverting output olp Level Intermediate Input input of Shifting stage stage stage stage Inverting inpot Dual input Dual - input complementary such as balanced unbalanced emitter symmetry. output output follower push-pull Differential Differential Using Const Amplifia Amplifier Ampli fien CULLENT Source Input stage: the input stage requires high input impedance to avoid loading on the sources. It nequines two input terminals: 9t also grequizes low output impedance. All such nequirements are achieved by using the dual input, balanced output differential amplifien as the input stage. The function of a differential amplifier is to amplify the difference two inpot signals. The differential between the amplifier has high input impedance. This stage provides most of the voitage gain of the amplifier Intermediate stage : the output of the input stage drives the next stage which is a intermediate stage. This is another differential amplifier with Dual input unbalanced output ie. single ended output. The overall gain requirement of the Op-Amp is Very high. The input stage alone cannot provide such a high gain. The main function of the Intermediate stage is to provide an additional voltage gain required. practically the intermediate stage is not a single amplifier but the chain of cascaded amplifiers called as multi-stage Amplifiers. 3) Level shifting stage :

All the stages are directly coupled to each other. As the op-Amp amplifies dic signals also, the coupling capacitons are not used to cascade the stages. Hence the dc quiescent voltage level of previous stage gets applied as the input to the next stage. Hence stage by stage dc level increases well above ground rever potential. such a high dic level may drive the transistors into saturation. This further may cause distortion in the output due to clipping. This may limit the maximum ac output voltage swing with out any distortion. Hence before the output stage, it is necessary to bring such a high dc voltage level to zero volts with respect to ground.

The level shifter stage brings the dc level down to ground potential, when no signal is applied at the input terminals then the signal is given to the last stage which is the output stage.

output stage :

The basic requirements of an output stage are low output impedance, large ac output Voltage swing and high current source and sinking capability.

The push pull complementary amplifier meets all these requirements and hence used as an output stage. This stage increases the output voltage swing and keeps the voltage swing symmetrical with respect to ground. This stage raises the current supplying capability of the OP-Amp. Differential Amplifier !

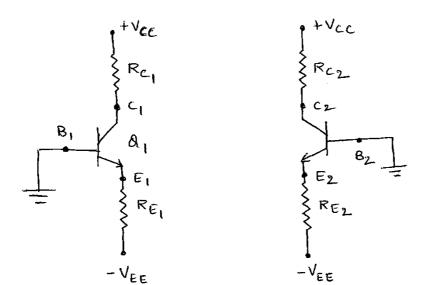

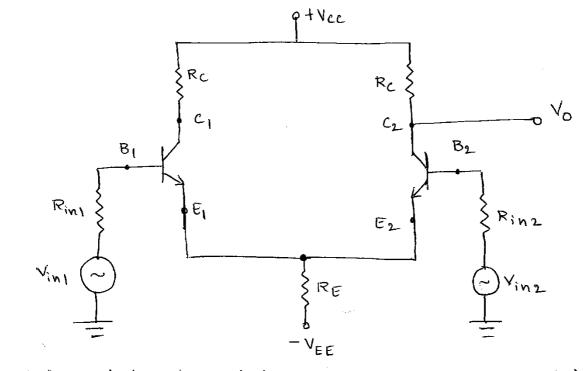

Let us consider the emitter biased circuit. Figure below shows two emitter identical emitter - biased cincuits in that transistor a, has the same characteristic as transiston Q2. RE1 = RE2, RC1 = RC2 and the magnitude of tVcc is equal to the magnitude of -VEE Here the supply voltages trac and -VEE are mean measured with nespect to ground.

Fig(a): Two identical emitter - biased Circuits

9 + Vcc Fig(b) : Dual input R<sub>L</sub> } Rc balanced output C2\_ c<sub>1</sub> B2diff amplifiu 22 ۹, B١ E2 E,  $\begin{cases} R_E = R_E, \\ R_E, \end{cases}$  $-V_{EE}$

the two circuits of fig(a) are reconnected to obtain a single circuit as shown in fig(b).

the differential amplifier of fig(b) amplifies the difference between two input signals Vin1 and Vin2. The differential amplifier is also neferred to as difference amplifier.

Differential Amplifier Circuit configurations : the four differential amplifier configurations are 1. Dual input, balanced output differential amplifier 2. Dual input, unbalanced output differential amplifier 3. single input, balanced output differential amplifier 4. Single input, unbalanced output differential amplifier sf we use two input signals, the configuration

is said to be dual input, otherwise it is a single input configuration.

gf the output is measured between two collectors it is referred to as a balanced output, because both collectors are at the same dc potential with nespect to ground.

of the output is measured at one of the collectors with respect to ground, the configuration is called an unbalanced output. i) Dual input, Balanced output Differential Amplifier Figure below shows the dual input balanced output differential amplifier. q+Vcc

Figl@). Dual input, balanced output differential Amplifier there the output Vo is measured between the two collectors C1 and C2 which are at the same dc potential. Because of the equal dc potential at the two collectors with respect to ground, the output is referred to as a balanced output.

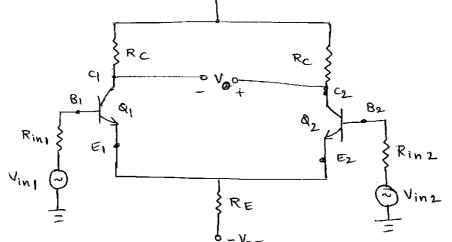

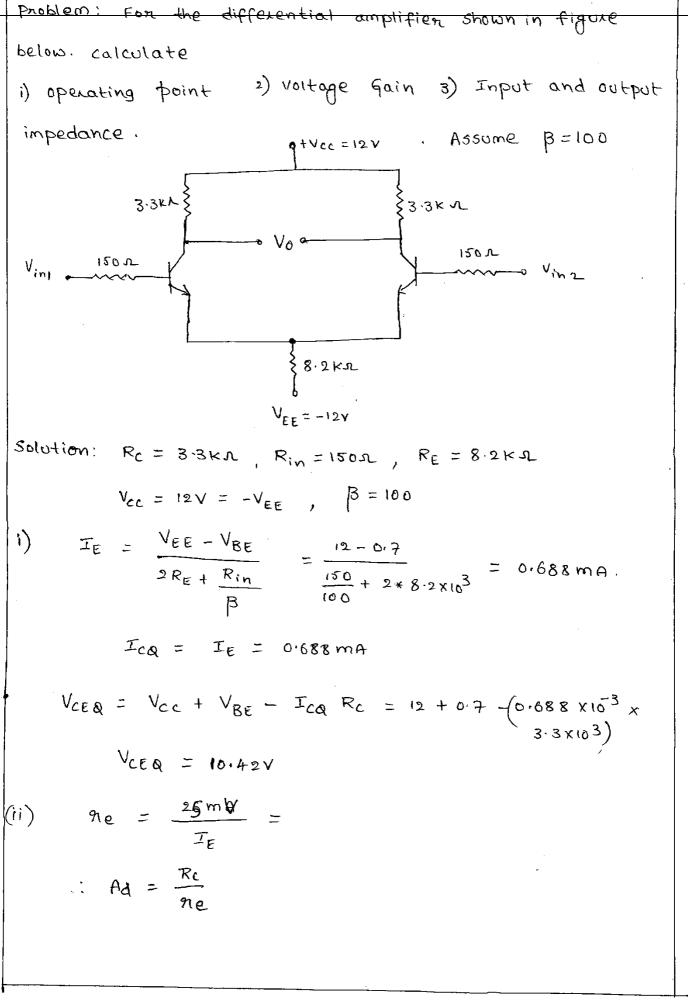

De Analysis:

To determine the operating values (Icq and Vecq) for

the differential amplifier of fig(a), it is needed to

obtain a dc Equivalent circuit. The dc equivalent circuit

can be obtained Simply by reducing the input Signals

Vini and Vinz to zero. The dc Equivalent circuit is

shown in figure (b).

since both emitter-biased junctions of the differential

amplifier are symmetrical, the operating point

(Vecq, Icq), for only one section can be determined.

(Vecq, Icq), for only one section can be determined.

We a size and Icq can then be used for transistor

$$Q_2$$

also.

Applying KVL to the base emitter loop of the

transistons  $Q_1$

$o = Rin TB + VBT + 2 IERE - VEE  $\longrightarrow 0$

But  $Ic = BIB$  since  $Ic = IE$

$IE = Bac TB  $\Rightarrow$   $IB = \frac{TE}{Bac} \longrightarrow 0$

But  $Fc = BIB$  since  $Ic = IE$

$IE = Rac TB  $\Rightarrow$   $IB = \frac{TE}{Rac} \longrightarrow 0$

$Equivalent is the termined is transistor  $R_1$

$VEE = VBE + 2RE + 2RE TE + Rin TE = Rac TB  $\Rightarrow$   $IB = \frac{TE}{Rac} + \frac{Rin}{Rac} = \frac{Rac}{Rac} = \frac{VEE - VBE}{Rac} + \frac{Rin}{Rac} = \frac{Rac}{Rac} = \frac{Rac}{Rac} = \frac{Rac}{R$$$$$$

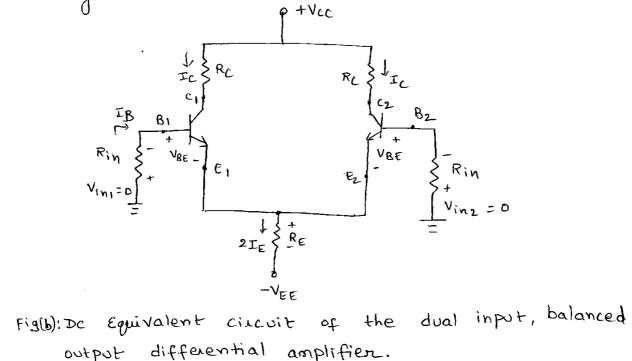

Emitten soment in transistors & and \$2 Rin << 2 RE, therefore Eq. 3 can be written as Generally Pac  $I_{E} = \frac{V_{EE} - V_{BE}}{2R_{E}} \longrightarrow (4)$ By selecting the proper value of RE, the desired Value of emitten connent for a known value of -VEE. The voltage at the emitten of transiston Q, is approximately equal to -VBE, of we assume that Voltage drop across Rin to be neglegibly small.  $V_c = V_{cc} - I_c R_c$ But VCE = VC - VE  $V_{CE} = \left( V_{CC} - I_C R_C \right) - \left( -V_{BE} \right)$  $V_{CE} = V_{CC} + V_{BE} - I_{C}R_{C} \longrightarrow \textcircled{S}$ Hence for both transistons, the Ica and Vcea by Equations (4) and (5) can be determined because the operating point  $I_E = I_{CQ}$  and  $V_{CE} = V_{CEQ}$ . Ac analysis : To perform ac analysis to derive the expression for the Voltage gain Ad and the input mesistance Ri of the differential amplifier shown in figure (a) i set the dc voltages truck and -VEE at Zeno 2. substitute the small - signal T-equivalent models for the transistons.

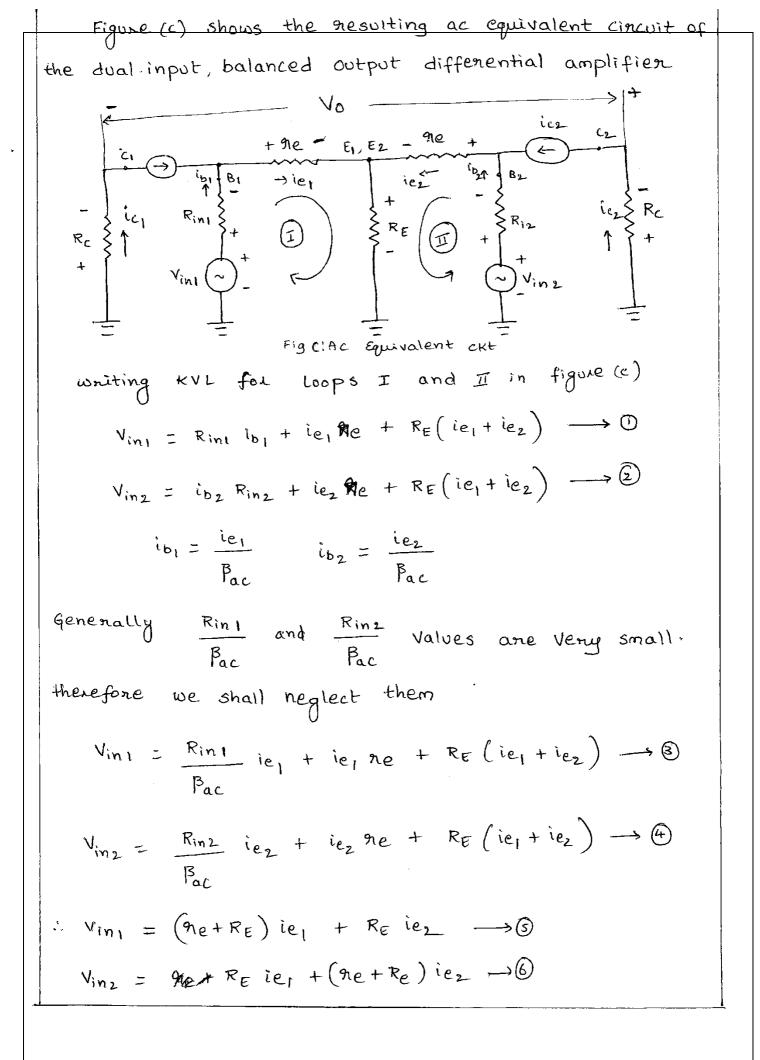

Equations (5) and (6) can be solved simulaneously

for ie, and ie, by using Chamen's gule.

$$ie_{1} = \frac{\Delta_{1}}{\Delta} = \frac{\begin{vmatrix} Vin_{1} & RE \\ \\ Vin_{2} & \eta e + RE \end{vmatrix}}{\begin{vmatrix} \eta e + RE & RE \\ \\ RE & \eta_{e} + RE \end{vmatrix}}$$

$$ie_{1} = \frac{(\eta e + RE) Vin_{1} - RE Vin_{2}}{(\eta e + RE)^{2} - (RE)^{2}} \longrightarrow (3)$$

$$ie_{2} = \frac{\Delta_{2}}{\Delta} = \frac{\begin{vmatrix} \eta e + RE \\ \\ RE \\ \\ \eta e + RE \\ \end{vmatrix}}{\begin{vmatrix} \eta e + RE \\ \\ RE \\ \\ \eta e + RE \\ \end{vmatrix}}$$

The output voltage

$$V_0 = V_{c_2} - V_{c_1}$$

$V_0 = -ic_2 R_c - (-ic_1 R_c)$

$V_0 = R_c (ic_1 - ic_2)$

$V_0 = R_c (ie_1 - ie_2) \longrightarrow (9)$

substituting the current relations  $i_{e_1}$  and  $i_{e_2}$  in  $\epsilon_q(9)$  we get

$$V_{0} = R_{c} \left[ \frac{\left( n_{e} + R_{E} \right) V_{in1} - R_{E} V_{in2}}{\left( n_{e} + R_{E} \right)^{2} - R_{e}^{2}} - \frac{\left( n_{e} + R_{E} \right) V_{in2} - R_{E} V_{in1}}{\left( n_{e} + R_{E} \right)^{2} - R_{e}^{2}} \right]$$

$$V_{0} = \frac{R_{c}}{\eta_{e}} \left( \frac{V_{in1} - V_{in2}}{V_{in1}} \right)$$

Let  $V_{d} = V_{in1} - V_{in2}$ , then

$$V_{0} = \frac{R_{c}}{\eta_{e}} V_{d} \implies A_{d} = \frac{V_{0}}{V_{d}} = \frac{R_{c}}{\eta_{e}} \longrightarrow (0)$$

The voltage gain equation of the differential amplifier is independent of RE.

2. Differential input Resistance :

Differential input resistance is defined as the equivalent resistance that would be measured at either input terminals with the other terminal grounded.

$$R_{i1} = \left| \frac{V_{in1}}{i_{b_1}} \right| V_{in2} = 0$$

$$R_{i1} = \left| \frac{V_{in1}}{T_{e_1}/\beta_{ac}} \right| = \frac{\beta_{ac} V_{in1}}{(\eta_{e} + R_E) V_{in1} - R_E(o)} - \frac{\beta_{ac} V_{in1} - R_E(o)}{(\eta_{e} + R_E)^2 - R_E^2}$$

$$R_{i1} = \frac{\beta_{ac} V_{in1} - R_E(o)}{(\eta_{e} + R_E)}$$

$$R_{i1} = \frac{\beta_{ac} V_{in1} - R_E(o)}{(\eta_{e} + R_E)}$$

$$R_{i1} = \frac{\beta_{ac} \quad \Re(n_e + 2R_E)}{(n_e + R_E)}$$

$R_E \gg \pi e$  which implies that  $\pi e + 2R_E \simeq 2R_E$  $\pi e + R_E \simeq R_E$

$$R_{i1} = \frac{\beta_{ac}}{R_E} \frac{\beta_{e}}{R_E}$$

$R_{i1} = 2\beta_{ac} g_e$

Similarly Riz = 2 Bac ne.

output Resistance :

output nesistance is defined as the equivalent nesistance that would be measured at either output terminal with nespect to ground.

$$R_{01} = R_{02} = R_{C}$$

Inventing and Non inventing Inputs:

In the differential amplifier circuit • the input voltage Vini is called the non inventing input because a positive voltage Vini acting alone produces a positive output voltage.

$$V_0 = \frac{R_c}{ne} (V_{in1} - o) = \frac{R_c}{ne} V_{in}$$

Similarly the positive Voltage Vinz acting alone produces a negative output Voltage, hence Vinz is called inventing input.

$$V_0 = \frac{R_c}{\eta_e} \left( 0 - V_{in} L \right) = - \frac{R_c}{\eta_e} V_{in} 2$$

common mode Rejection Ratio :

An important characteristic of the dual input balanced output differential amplifier is its ability to supress undesired disturbances that might be amplified along with the desired signal. when the matched pair of transistons is used in the differential amplifien, the unwanted signals would appear as common to both input bases, and the net output would be theoretically zero.

the practical effectiveness of rejecting the common signal depends on the degree of matching between the two common - emitter stages forming the differential amplifier.

In otherwords, the more closely equal are the currents in the input transistors Q, and Q2. The better is the common mode signal rejection.

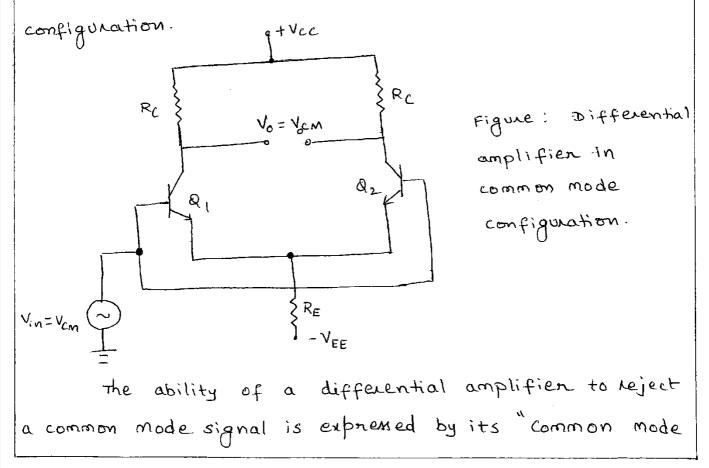

when the same voltage is applied to both input terminals of a differential amplifier, the differential amplifier is said to operate in the common mode

Rejection Ratio" (CMRR). It is the Ratio of differential

gain ADM to the Common Mode gain Acm

$$CMRR = \frac{ADM}{ACM}$$

The common mode voltage gain Acm can be as

follows the known voltage Acm to both input tenninals

of the differential amplifier in applied as shown in

figure above - Here Acm =  $\frac{Vocn}{Vcm}$

Ideally & Acm to be zero that in Vocm = 0V.

In other words CMRR is ideally infinity thus it is

advantageous to use a differential amplifier with

higher CMRR since this amplifier is better able to

hejest Common mode Signals.

Input output wave forms

Voltage 1

$Vo = Vcz - Vcl$

$Vo = Vcz - Vcl$

Dual input unbalanced output Differential Amplifier:

In this configuration two input signals are used . however the output is measured at only one of the two collectors with respect to ground. The output is referred to as an unbalanced output,

Let us assume that the output is measured at the collector of transiston Q2 with respect to ground. De Analysis:

$$I_E = I_{CQ} = \frac{V_{EE} - V_{BE}}{2R_E + \frac{R_{in}}{\beta_{dC}}}$$

Fig(a): Dual input unbalanced output Differential Amplifier Ac Analysis: Fig below shows the ac equivalent Cincuit of the dual input, unbalanced output differential

Generally RE>>ne, hence het RE = RE, het 2RE = 2RE  $N_0 = R_c \frac{R_E V_{in1} - R_E V_{in2}}{2 \Re e R_E}$  $V_0 = \frac{R_c}{2 \eta_0} \left( V_{in1} - V_{in2} \right)$  $A_d = \frac{V_0}{V_d} = \frac{R_c}{29e}$ Thus the voitage gain of the dual input unbalanced output differential amplifier is half the gain of the dual input balanced output differential amplifier. Differential input resistance :  $R_{i_1} = R_{i_2} = 2 \beta_{a_1} g_{e_2}$ Differential output resistance  $R_{01} = R_{02} = R_{L}$ Level Translator (Level shifting stage): Because of the direct coupling, the dc level at the emitters rises from stage to stage. This increase in de level tends to shift the operating point of the succeeding stages and therefore limits the output voltage swing and may even distort the output signal the voltage at the output terminal of the Second stage is well above ground (ov). This dc level is undesinable because it tends to limit the peak to peak output voltage swing without distortion and

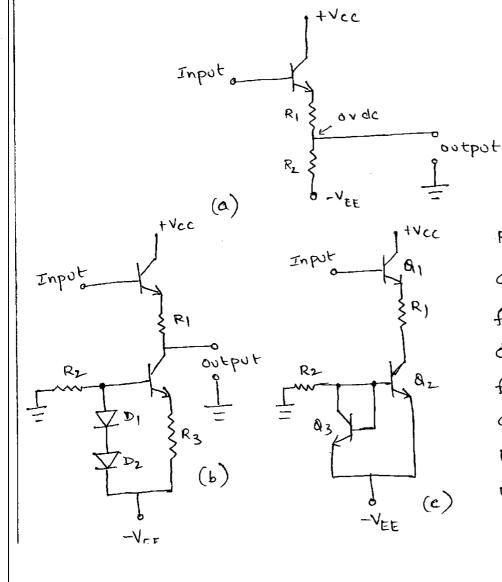

also contributes to the error in the dc output signal. therefore a final stage should be included to shift the output dc level at the second stage down to about zero volts to ground. such a stage is neferned to as a level translator or shifter. Thus in the cascaded differential amplifier, to shift the output dc level down to zero volts, the final stage must be followed by a level translator circuit.

A simplest level translator circuit is an emitter follower with a Voltage divider circuit. is shown in figure below.

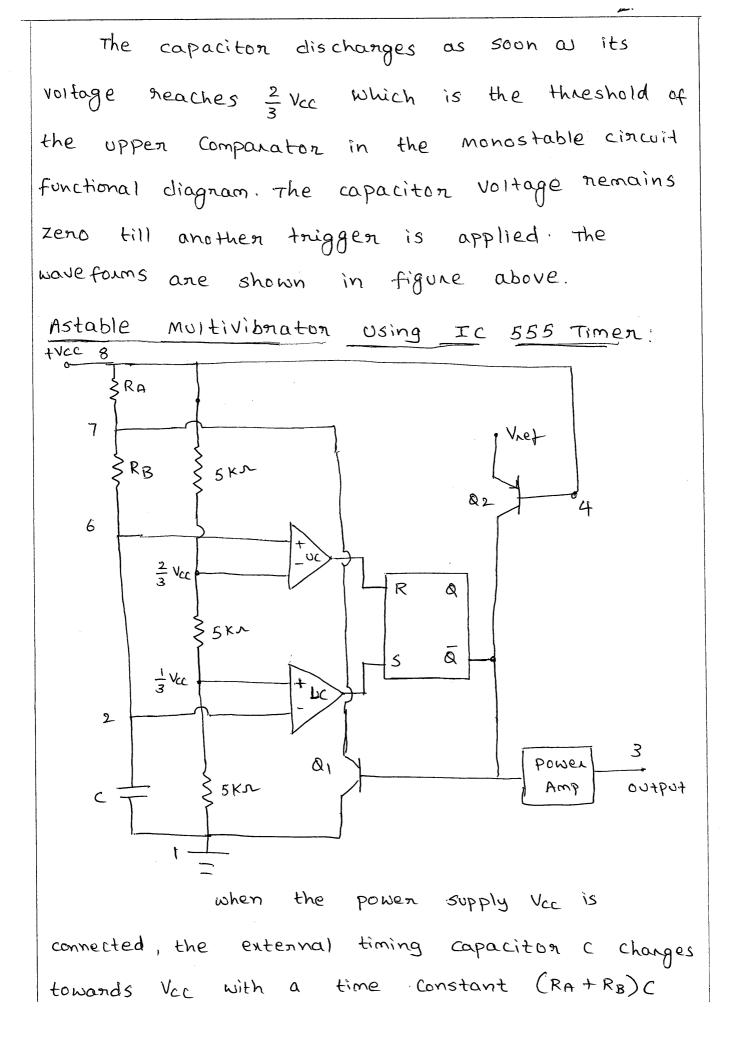

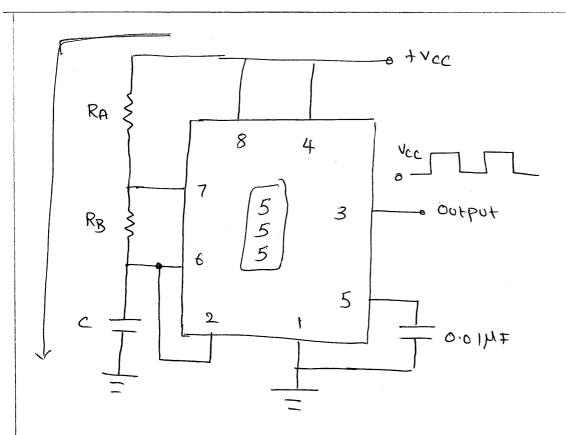

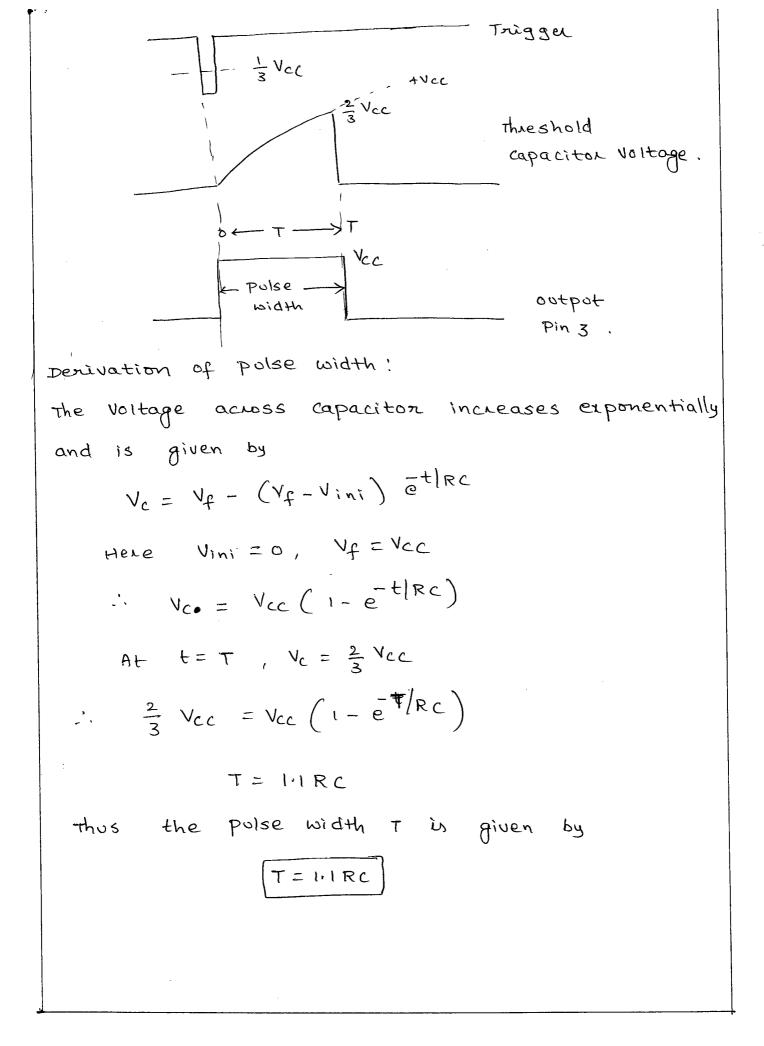

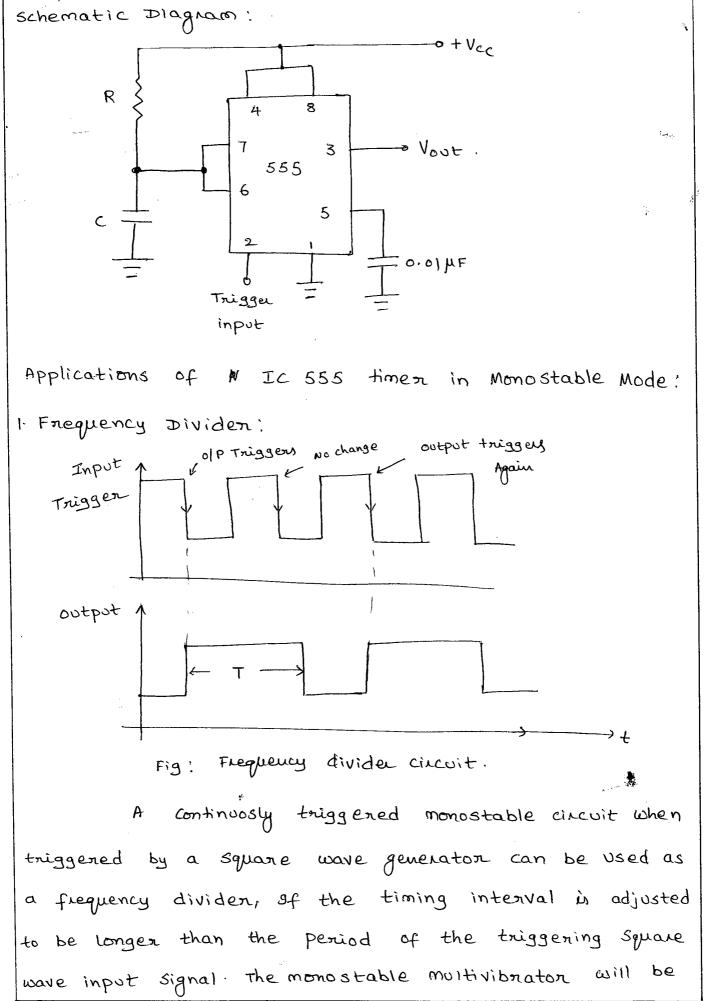

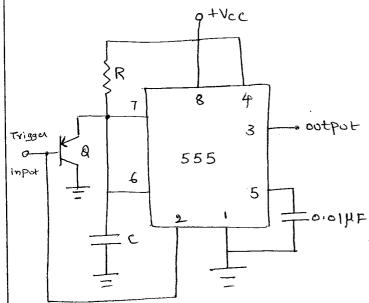

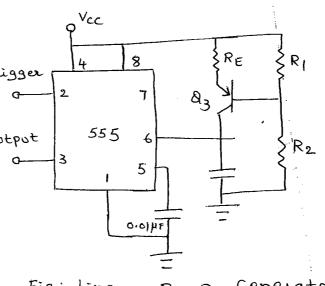

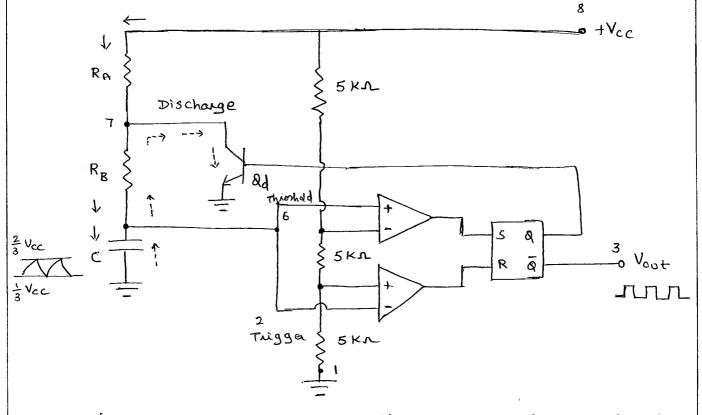

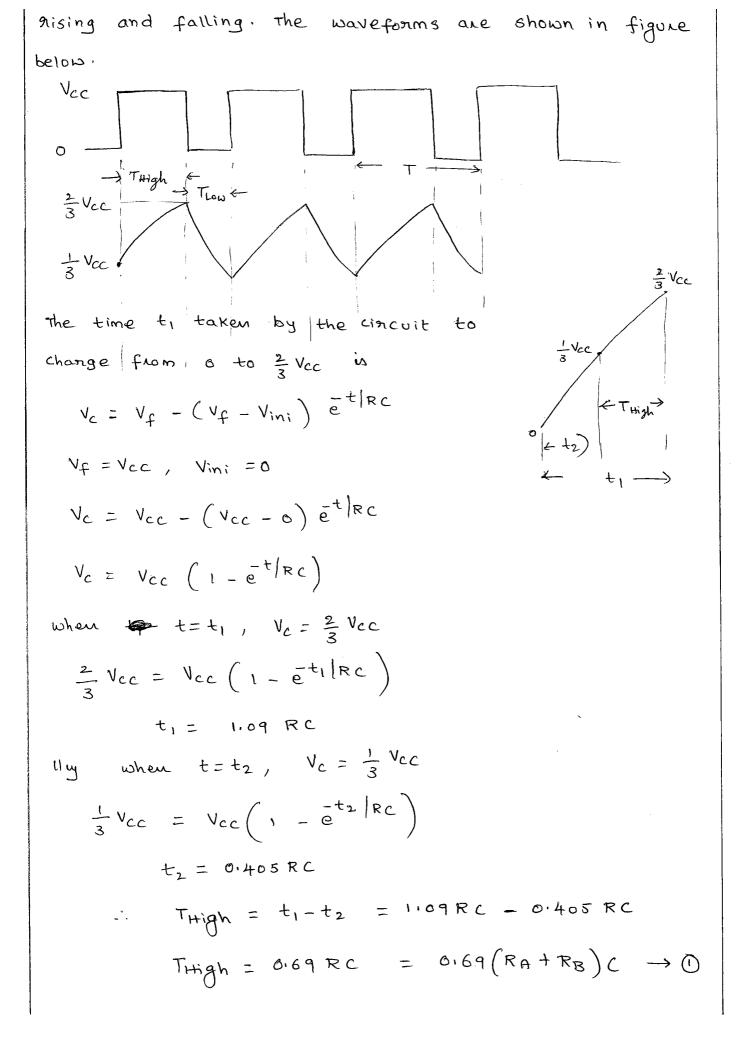

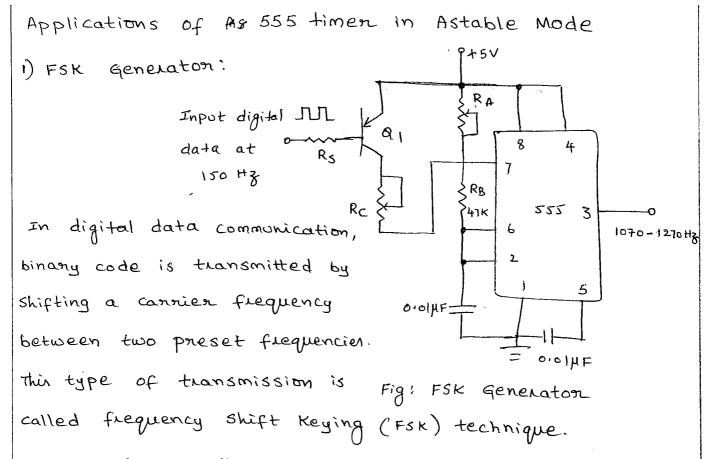

Fig: Level translator Circuits (a) Emitter Follower with voltage divider (b) Emitter follower with Constant Current bias (c) Emitter follower with Current missor.

As the configuration is dual input balanced output

iii)

$$R_1 = 29e\beta = 2x$$

(iv)  $R_0 = R_c = 33KR$ .

Problem:  $9f$  the base converts for the emitter (coupled

thansistons of a differential amplifier are  $18\mu A$

and  $22\mu A$ . Determine

i) Input bias connent (ii) Input affset Cunnent

for an op-Amp.

Solution:  $T_{D_0} = 18\mu A$ ,  $T_{D_0} = 22\mu A$

(i) Input bias convert  $T_D = \frac{T_{D_0}^+ + T_D D}{2} = \frac{18 + 22}{2} = 20\mu A$

(ii) Input bias convert  $T_D = \frac{T_{D_0}^+ + T_D D}{2} = \frac{18 + 22}{2} = 20\mu A$

(iii) Input offset convert

$T_{IOS} = |T_D^+ - T_{D_0}| = |18 - 22| = 4\mu A$ .

Problem:

An op-Amp operates as a unity gain buffer

with  $3v$  (peak to beak) square wave input  $3f$

op-Amp is ideal with slew state  $0.5v/\mu S$ . Find the

maximum frequency of operation.

Solution:  $V_{P,P} = 3v = V_P = \frac{V_P - P}{2} = \frac{3}{2} = 1.5v$

$f_{max} = \frac{Slew rate}{2\pi VP} = \frac{0.5 \times 10^6}{2\pi \times 10^5} = 53.85 \text{ KHz}$

Problem: A square wave of peak to peak amplitude

of 750 mV has to be amplified to a peak to peak

amplitude of 38V, with a nine time of 415 µ sec on

less. Can IC 741 of Amp be used?

Solution:

$$SR = \frac{\Delta V}{\Delta t}$$

, IC 741 has  $SR = 0.5 V/\mu sec$

Now Rise time is the time nequined by the output

to Rise from 10% to 90% of its final value

$\Delta V = (0.9 - 0.1) 3.8 V = 3.04 V$ .

$\Delta t = 4.5 \mu sec$

$SR = \frac{\Delta V}{\Delta t} = \frac{3.04 V}{4.5 \mu} = 0.675 V/\mu sec$ .

The slew Rate of IC 741 is 0.5 V/\mu sec advicts is

too low compared to what is nequined thence IC 741

op-Amp Cannot be used.

Problem: In negronse to a square wave input, the

output of an op-Amp changed from -3V to +3V over

a time interval of 0.25 V/AS. Determine the slew Rate

of the op-Amp.

Solution: change in output voltage = -3V to +3V

$dV_0 = 3-(-3) = 6V$

$dt = 0.25 V/\mu S$ .

$Slew Rate = \frac{dV_0}{dt} = \frac{6}{0.25 \mu S} = 24 V/\mu S$ .

problem: For the op-Amp configuration shown in figure below the gain required is 61. Determine the appro--priate value of feedback resiston Rf. Rf solution ! IKN Vn  $Gain = 1 + \frac{R_f}{R_1} \implies 61 - 1 = \frac{R_f}{R_1}$ solution :  $R_f = 60 R_i = 60 \times 1 \times 1 \times 1 = 60 \times 1$ problem: For an op-Amp having a slew rate of 3 1/45. what is the maximum closed loop voltage gain that can be used when the input signal Varies by 0.4V in 12 µsec? Solution!  $V_0 = A V_i$  $\frac{dv_0}{dF} = A \frac{dv_i}{dF}$ Slew late =  $A = \frac{dv_i}{dt} \Rightarrow A = \frac{SR}{dv_i}$  $=) A = \frac{3}{10^{-6}} = 90.$

problem: The common mode input to a certain differen--tial amplifier, having differential gain of 125 is 4 Sin 200TT V. Determine the common mode output if CMRR is GodB. solution: the CMRR in dB is  $60 = 20 \log \left| \frac{Ad}{0} \right|$  $\frac{Ad}{Ac} = 1000 \implies A_{c} = \frac{Ad}{1000} = \frac{125}{1000} = 0.125$ Hence the common mode output is = AcVc =  $0.125 (4 \sin 200\pi t) = 0.5 \sin(200\pi t) V$ problem: How fast can the output of an op-Amp change by IOV if its slew Rate is IV/µs. solution :  $SR = IV | \tilde{\mu}S$  $SR = \frac{\delta V_0}{\Delta L} \implies \Delta L = \frac{\Delta V_0}{SR}$  $\Delta t = \frac{10V}{1V|\mu s} = 10 \mu s$ thus 10 µsec will be required by an op-Amp to change output by lov.

| U | Ν | IT | -2 |

|---|---|----|----|

|---|---|----|----|

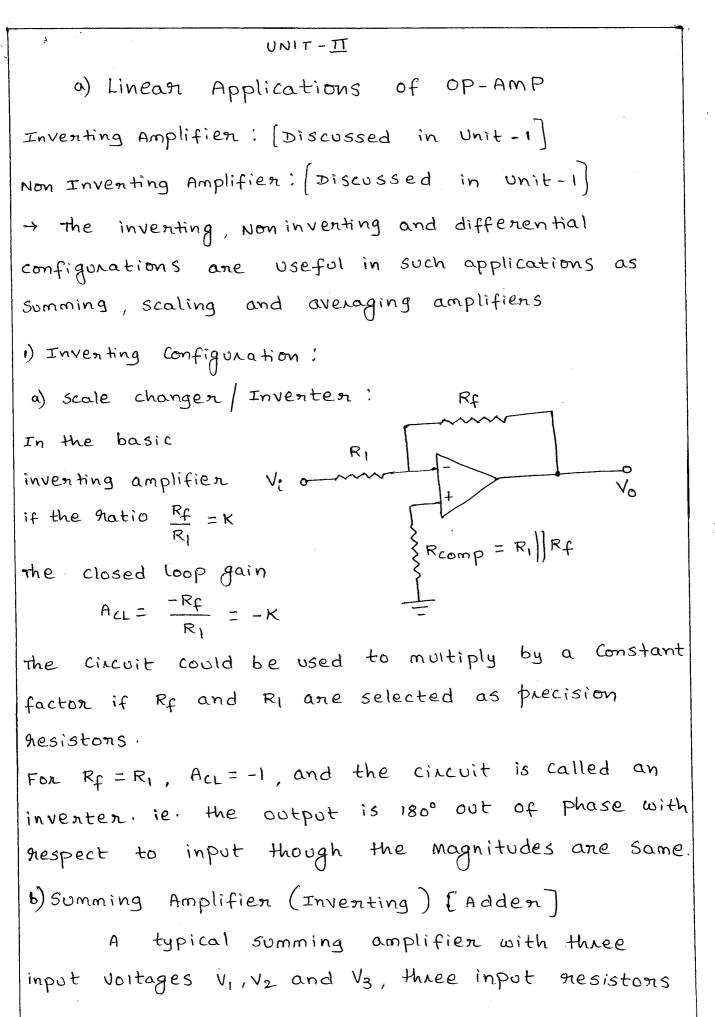

$R_1, R_2, R_3$  and a feedback nesiston  $R_f$  as shown in figure below.

the following analysis is cannied out assuming that the op-Amp is an ideal one ie  $A_{0L} = \infty$  and  $R_i = \infty$ . since the input bias current is assumed to be zero, there is no voltage dramp across the resistor  $R_{comp}$  and hence the non inverting input terminal is at ground potential.

the voitage at node 'a' is zero as the non inventing input terminal is grounded. The hodal equation by KCL at hode 'a' is

$$\frac{V_{1}-0}{R_{1}} + \frac{V_{2}-0}{R_{2}} + \frac{V_{3}-0}{R_{3}} = \frac{0-V_{0}}{R_{f}}$$

$$\implies V_{0} = -\left(\frac{R_{f}}{R_{1}}V_{1} + \frac{R_{f}}{R_{2}}V_{2} + \frac{R_{f}}{R_{3}}V_{3}\right)$$

Hence the output is invested and the weighted sum of the inputs.

If  $R_1 = R_2 = R_3 = R_f \implies V_0 = -(V_1 + V_2 + V_3)$ Hence the output is invested and sum of 3 inputs.

c) Avenage cincuit:

In fig(a), if

$$R_1 = R_2 = R_3 = R$$

$\frac{R_f}{R} = \frac{1}{n} \implies n = number of inputs$

ef  $n=3 \implies \frac{R_f}{R} = \frac{1}{3}$

From fig(a) the output  $V_0 = -\left(\frac{R_f}{R_1}V_1 + \frac{R_f}{R_2}V_2 + \frac{R_f}{R_3}v_3\right)$

$\Rightarrow V_0 = -\left(\frac{R_f}{R}V_1 + \frac{R_f}{R}V_2 + \frac{R_f}{R}V_3\right)$

$V_0 = -\left(\frac{1}{3}V_1 + \frac{1}{3}V_2 + \frac{1}{3}V_2\right)$

$V_0 = -\left(\frac{V_1 + V_2 + V_3}{3}\right)$

output is inverted, and average of three inputs.

(a) Summing Amplifier (Non inventing) [Adden]:

A summer that gives a non invented sum is

the non inventing Summing amplifier. st is shown in

figure below.

$V_1 = \frac{V_1}{R_1}V_2$

$V_2 = \frac{V_1}{R_2}V_3$

Here  $V_0 = \left(1 + \frac{R_f}{R}\right)V_0$

writing KCL at non inventing input  $\frac{V_1 - V_a}{R_1} + \frac{V_2 - V_a}{R_2} + \frac{V_3 - V_a}{R_2} = 0$  $\Rightarrow V_a = \frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3}$  $\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{D}$ Now  $\varepsilon_q(1) \Rightarrow V_0 = \left(1 + \frac{R_f}{R}\right) \left(\frac{\frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3}}{\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}}\right) \rightarrow (2)$ Vo is noninvented and weighted sum of inputs. Let  $R_1 \neq R_2 = R_3 = R$ ,  $R_f = 2R$  $V_0 = (V_1 + V_2 + V_3)$ output is non invented, we sum of inputs b) Avenaging Amplifien: From Eq (2) Let  $R_1 = R_2 = R_3 = R$  $V_0 = \begin{pmatrix} 1 + \frac{R_f}{R} \\ -\frac{1}{R} \end{pmatrix} \begin{pmatrix} \frac{V_1}{R} + \frac{V_2}{R} + \frac{V_3}{R} \\ -\frac{1}{R} + \frac{1}{R} + \frac{1}{R} \end{pmatrix}$  $V_0 = \left(1 + \frac{R_f}{R}\right) \left(\frac{V_1 + V_2 + V_3}{3}\right)$  $V_0$  is  $\left(1 + \frac{R_f}{R}\right)$  times average of all three inputs. problem: Design an adder circuit Using an OP-Amp to get the output expression as  $V_0 = -(0.1 V_1 + V_2 + 10 V_3)$  where  $V_1, V_2, V_3$ are inputs

Solution: Given

$$V_0 = -(0.1V_1 + V_2 + 10.V_3)$$

The output  $V_0$  of inventing summing amplifien

$V_0 = -\left[\frac{R_f}{R_1}V_1 + \frac{R_f}{R_2}V_2 + \frac{R_f}{R_3}V_3\right]$

Assume  $R_f = 10 KR$

$\Rightarrow \frac{R_f}{R_1} = 0.1 \Rightarrow R_1 = 100 KR$

$\frac{R_f}{R_2} = 1 \Rightarrow R_2 = 10 KR$

$\frac{R_f}{R_2} = 1 \Rightarrow R_2 = 10 KR$

$\frac{R_f}{R_3} = 10 \Rightarrow R_3 = 1KR$

$\frac{R_f}{R_3} = 10 \Rightarrow R_3 = 1KR$

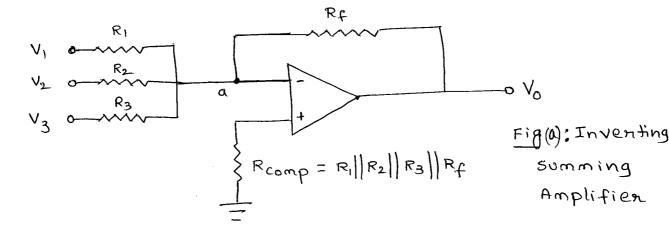

$(3) Differential Configuration:

$a \text{ basic differential amplifien can be used as a subtractor:}$

$a \text{ basic differential amplifien can be used as a subtractor as shown in figure below.}$

$g_f all resistons are equal in value, then  $V_2 = R$

the output Voltage  $V_1 = V_1$

$V_0 = \frac{R_1}{R} = 10$

$V_{01} = 2V_a = 2XV_1 = V_1$

$V_1 = 2V_a = 2XV_1 = V_1$

$\Rightarrow V_0 = -V_1$$$

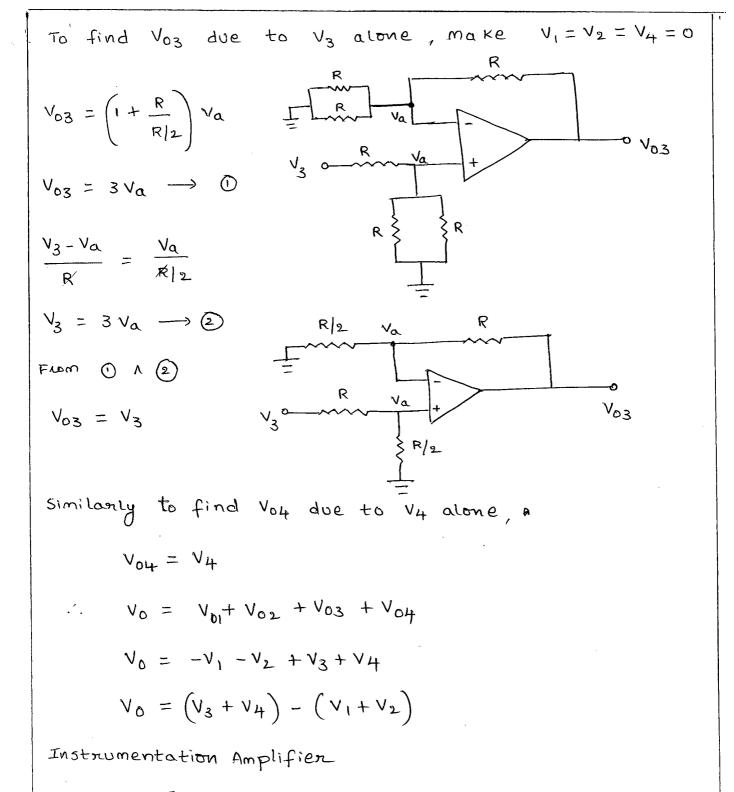

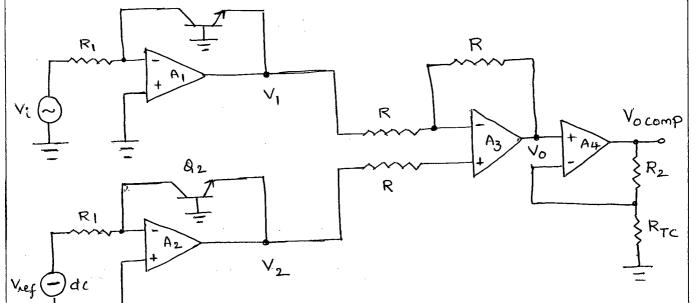

In a number of Industrial and Consumer applications, It is required to measure and control physical quantities. Some typical examples are measurement and control of temperature, humidity, light intensity, water flow etc. These physical quantities are usually measured with the help of transducers. The output of

transducer has to be amplified, so that it can drive

the indicator or display system. This function is

performed by an instrumentation amplifier. The important

features of an instrumentation amplifier are

i) High gain accuracy

2) High CMRR

3) High gain stability with low temp Co-efficient

4) Low de affset

5) Low output impedance.

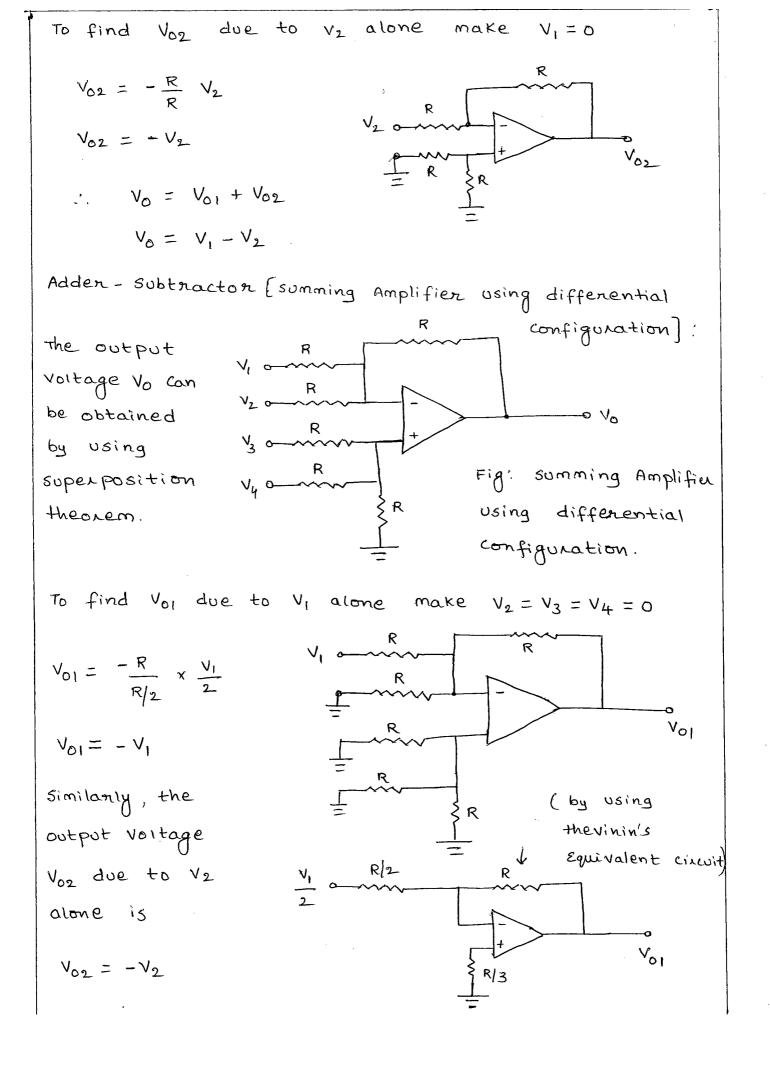

consider the basic differential amplifier shown in

figure below.

$$V_2 = \frac{R_1(ue)}{V_1} + \frac{V_2}{V_2} + \frac{R_2(uex)}{V_1} + \frac{V_2}{V_2} + \frac{R_1(ue)}{V_2} + \frac{V_2}{V_1} + \frac{R_2(uex)}{V_2} + \frac{V_2}{V_1} + \frac{R_2(uex)}{V_2} + \frac{V_2}{V_1} + \frac{R_2(uex)}{V_2} + \frac{R_1(ue)}{V_2} + \frac{R_2(uex)}{V_2} + \frac{R_2(uex)}{V_2} + \frac{R_2(uex)}{V_2} + \frac{R_2(uex)}{V_2} + \frac{R_1(uex)}{V_2} + \frac{R_2(uex)}{V_2} + \frac{R_2$$

$$V_{02} \text{ due to } V_{2} \text{ alone}, \text{ make } V_{1} = 0$$

$$V_{02} = -\frac{R_{2}}{R_{1}} V_{2}$$

$$V_{2} \xrightarrow{R_{1}} V_{2} \xrightarrow{R_{2}} V_{2}$$

$$V_{0} = V_{01} + V_{02}$$

$$V_{0} = -\frac{R_{2}}{R_{1}} V_{2} + V_{1} \left(1 + \frac{R_{2}}{R_{1}}\right) \left(\frac{1}{1 + \frac{R_{3}}{R_{4}}}\right)$$

$$V_{0} = -\frac{R_{2}}{R_{1}} \left(-V_{2} + V_{1} - \frac{R_{1}}{R_{2}} \left(1 + \frac{R_{2}}{R_{1}}\right) \left(\frac{1}{1 + \frac{R_{3}}{R_{4}}}\right)\right)$$

$$V_{0} = -\frac{R_{2}}{R_{1}} \left(-V_{2} + V_{1} - \frac{R_{1}}{R_{2}} \left(1 + \frac{R_{2}}{R_{1}}\right) \left(\frac{1}{1 + \frac{R_{3}}{R_{4}}}\right)\right)$$

$$V_{0} = -\frac{R_{2}}{R_{1}} \left(V_{1} \left(1 + \frac{R_{1}}{R_{2}}\right) - \frac{1}{\left(1 + \frac{R_{3}}{R_{4}}\right)}\right) \xrightarrow{T}$$

$$\Psi_{0} = -\frac{R_{2}}{R_{1}} \left(V_{1} \left(1 + \frac{R_{1}}{R_{2}}\right) - \frac{1}{\left(1 + \frac{R_{3}}{R_{4}}\right)}\right)$$

$$\Psi_{0} = -\frac{R_{2}}{R_{1}} \left(V_{1} \left(1 + \frac{R_{1}}{R_{2}}\right) - \frac{1}{\left(1 + \frac{R_{3}}{R_{4}}\right)}\right)$$

In fig(a) source  $V_1$  sees an input impedance =  $R_3 + R_4$ (101KL) and the impedance seen by source  $V_2$  is only  $R_1$ (1KL), this low impedance may load the signal source heavily therefore, high resistance buffer is used proceeding each input to avoid this loading effect as shown in fig(b) below.

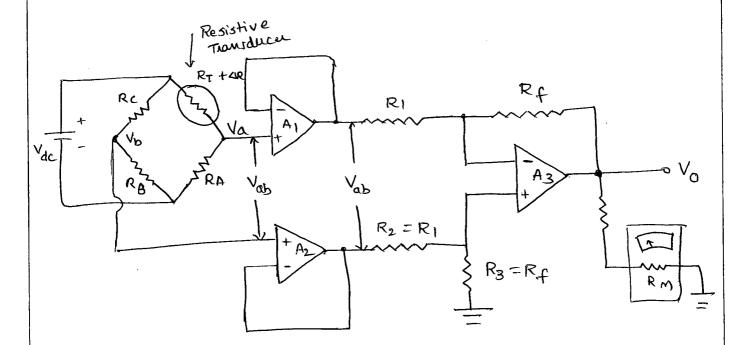

The op-Amps A1 and A2 have differential input Voltage as zero. For  $V_1 = V_2$ , that is, under common mode condition the voltage across R will be zero. As no current flows through R and R' the non inventing amplifier A, acts as voltage follower, so its output  $V_2' = V_2$ similary  $V_1' = V_1$ . However if  $V_1 \neq V_2$ , current flows in R and R' and

$(v_2' - v_1') > (v_2 - v_1)$ . There fore this circuit has differential gain and CMRR more compared to the single op-Amp cincuit (fig(a)). The output voltage Vo can be calculated as follows. R2  $\mathbb{R}^1$   $\mathbb{V}_2^1$ A3 ٧۵  $\mathbb{R}^{1}$ RI Fig(b): An improved instrumentation Amplifier compare \$ opAmp - 3 with op-Amp in fig(a), then V6 7 output Vo can be witten as (by comparing eq)  $V_0 = \frac{R_2}{R_1} \left( V_1^{\dagger} \left( 1 + \frac{R_1}{R_2} \right) \frac{1}{\left( 1 + \frac{R_1}{R_2} \right)} - V_2^{\dagger} \right)$  $V_0 = \frac{R_2}{R_1} \left( V_1' - V_2' \right) \longrightarrow 3$ since no concent flows into op-Amp, the concent I flowing (upwards) in R is  $I = \frac{V_1 - V_2}{D}$  and passes through the resistor R'.  $V_2 = IR' + V_2' \implies V_2' = V_2 - IR' = V_2 - \left(\frac{V_1 - V_2}{R}\right)R'$  $\therefore V_2' = -\frac{R'}{2} (V_1 - V_2) + V_2 \longrightarrow 4$  $\lim_{n \to \infty} V_{1} = -IR' + V_{1}' \implies V_{1}' = V_{1} + IR' = V_{1} + \left(\frac{V_{1} - V_{2}}{D}\right)R'$  $\therefore V_1' = \frac{R'}{2} (V_1 - V_2) + V_1 \longrightarrow \textcircled{5}$

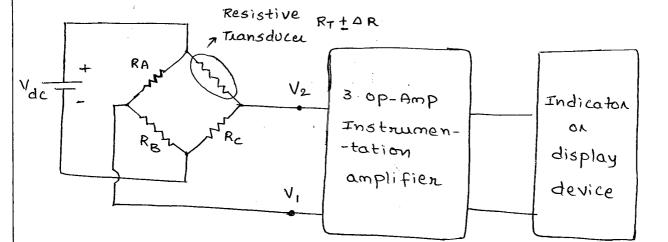

From Eq's (4) and (5), Eq (3) becomes  $V_{0} = \frac{R_{2}}{R_{1}} \left[ \frac{R'}{R} \left( V_{1} - V_{2} \right) + V_{1} + \frac{R'}{R} \left( V_{1} - V_{2} \right) - V_{2} \right]$  $V_{0} = \frac{R_{2}}{R_{1}} \left( \frac{2R'}{R} \left( V_{1} - V_{2} \right) + \left( V_{1} - V_{2} \right) \right)$  $V_{0} = \frac{R_{2}}{R_{1}} \left( 1 + \frac{2R^{1}}{R} \right) \left( V_{1} - V_{2} \right) \longrightarrow \textcircled{6}$ In  $\epsilon_{2}$  (6), 97 we choose  $R_{2} = R_{1} = 25 \text{ km}$ , R' = 25 km, R = 50 mthen a gain of 1001 Can be achieved. The difference gain of this instrumentation amplifier can be varied by neplacing the nesistance R by a potentiometer in fig(b). The resistance R, however should never be made zero, as this will make the gain infinity. To avoid such a situation, in a plactical circuit, a fixed resistance series with a potentiometer is used in place of Rin Figure (c) below shows a differential instrumentation amplifier using transducer bridge.

Fig(c): Instrumentation amplifier using transducer bridge the circuit uses a resistive transducer whose resistance changes ch as a function of the physical quantity to be measured. The bridge is initially balanced by a dc supply voltage  $V_{dc}$  so that  $V_1 = V_2$ . As the physical quantity changes, the resistance  $R_T$  of the transducer also changes, causing an unbalance in the bridge  $(V_1 \neq V_2)$ . This differential Voltage now gets amplified by the three op-Amp differential instrumentation Amplifier.

there are a number of practical applications of instrumentation amplifier with the transducer bridge, such as temperature indicator, temperature controller, light intensity meter etc.

Instrumentation Amplifier Using Transducer Bridge (&: Temperature measurement):

Fig: Differential instrumentation amplifier using a transducen bridge.

Figure shows a simplified differential instrumentation amplifier using a transducer bridge. A resistive transducer whose resistance changes as a function of some physical energy is connected in one and of the bridge with a small Circle around it and is denoted by  $(R_T \pm \Delta R)$  where  $R_T$  is the resistance of the transducer and  $\Delta R$  the change in resistance  $R_T$

the bridge in the circuit is de excited but could be ac excited as well. For the balanced bridge at some negenence condition

$$V_b = V_c$$

$$\frac{R_{b} V_{dc}}{R_{B} + R_{c}} = \frac{R_{A} V_{dc}}{R_{A} + R_{T}} \implies \frac{R_{c}}{R_{B}} = \frac{R_{T}}{R_{A}}$$

Generally resistons RA, RB and Rc are selected so that they are equal in value to the transducer resistance at some reference condition.

the bridge is balanced initially at a desired neference condition. However as the physical quantity to be measured changes, the nesistance of the transducer also changes, which causes the bridge to unbalance  $(Va \neq Vb)$

Let the change in resistance of transducer be DR. then

$$V_{a} = \frac{RA VdC}{RA + (R_{T} + \Delta R)}$$

$$V_{b} = \frac{R_{B} VdC}{R_{B} + RC}$$

$$V_{ab} = V_a - V_b$$

$$= \frac{R_A V_{dc}}{R_A + R_T + \Delta R} - \frac{R_B V_{dc}}{R_B + R_T}$$

HOWEVER of RA = RB = RC = RT = R, then

$$V_{ab} = - \frac{\Delta R V_{dc}}{2 (2R + \Delta R)}$$

the negative sign indicates that Va < Vb because of the increase in the Value of RT.

Temperature indicator: the above circuit can be used as a temperature indicator if the transducer in the bridge circuit is a thermistor and the output meter is calibrated in degrees celcius or Fahrenheit. The bridge can be balanced at a desired neference condition ( $\epsilon x 2 s^{\circ} c$ ). As the temperature varies from its reference value, the nesistance of the thermistor changes and the bridge becomes unbalanced. This unbalanced bridge inturn produces the meter movement. The meter can be calibrated to read a desired temp range by selecting an appropriate gain for the differential instrument ation Amplifier (meter movement &  $\Delta V_{0}$ ,  $\Delta V_{0} \propto \Delta R$ ] Hue  $\Delta R =$  temp co-efficient of (final temp - ref temp) Ac' Amplifier :

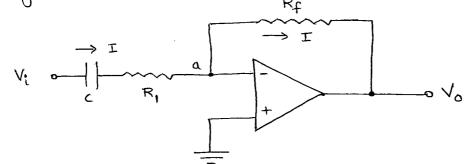

The inverting and non-inverting Op-Amp Amplifier Respond to both ac and dc signals. But to get the ac frequency response of an op-Amp on if the ac input signal is superimposed with dc level, it becomes essential to block the dc component. This is achieved by using an Ac amplifier with a coupling capacitor.

Ac amplifiens are of two types

1. Inventing ac Amplifier.

2. Non inventing ac Amplifier.

1. Inventing Ac amplifien:

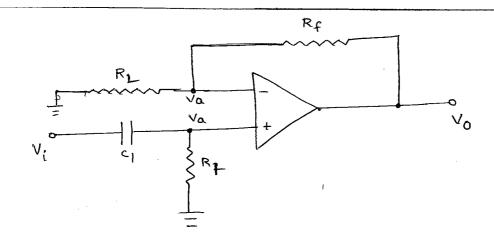

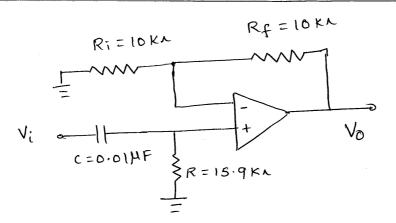

The circuit of inverting ac Amplifier is shown in figure below.

Fig : Inventing Ac Amplifien

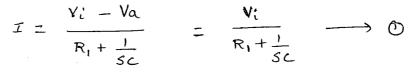

Again

$$I = \frac{V_a - V_o}{R_f} \implies \frac{-V_o}{R_f} \longrightarrow \textcircled{2}$$

From (1) and (2)

$$-\frac{V_0}{R_f} = \frac{+V_i}{R_i + L_{sc}}$$

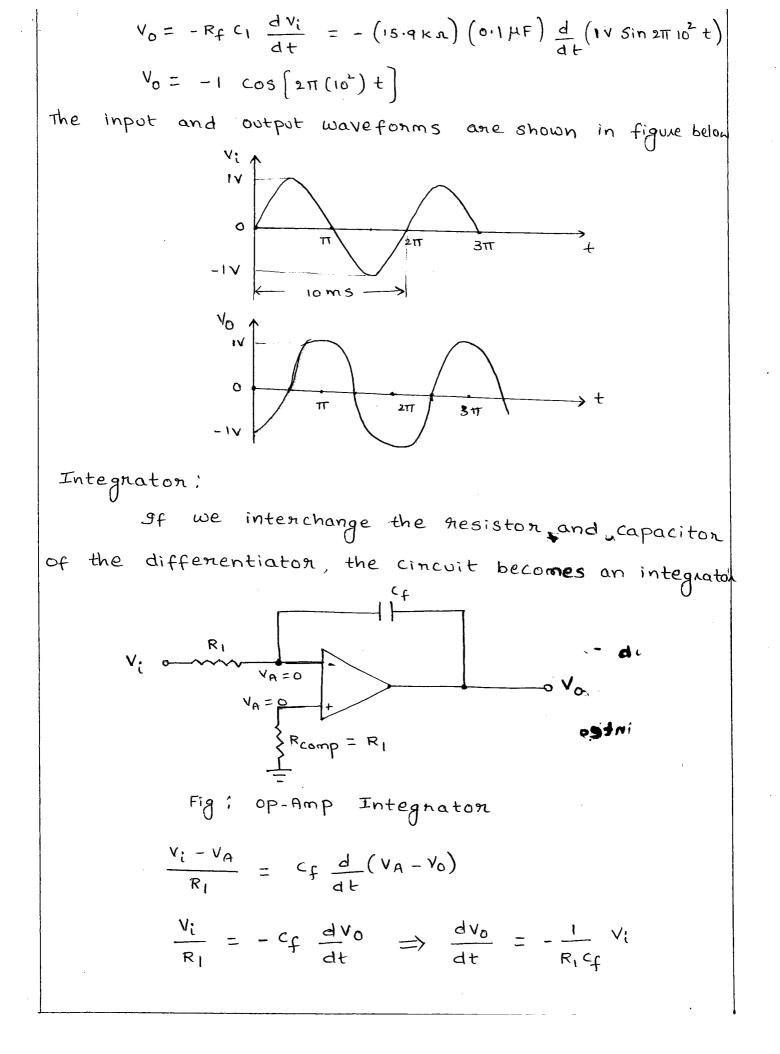

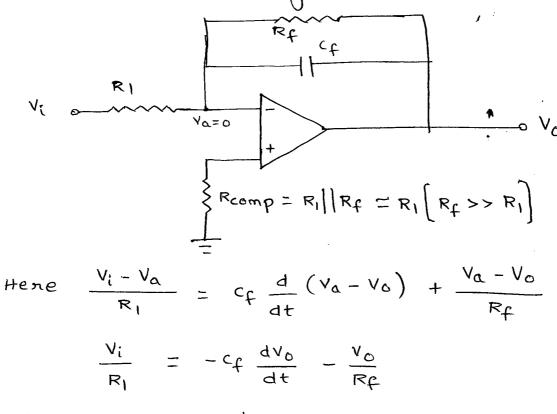

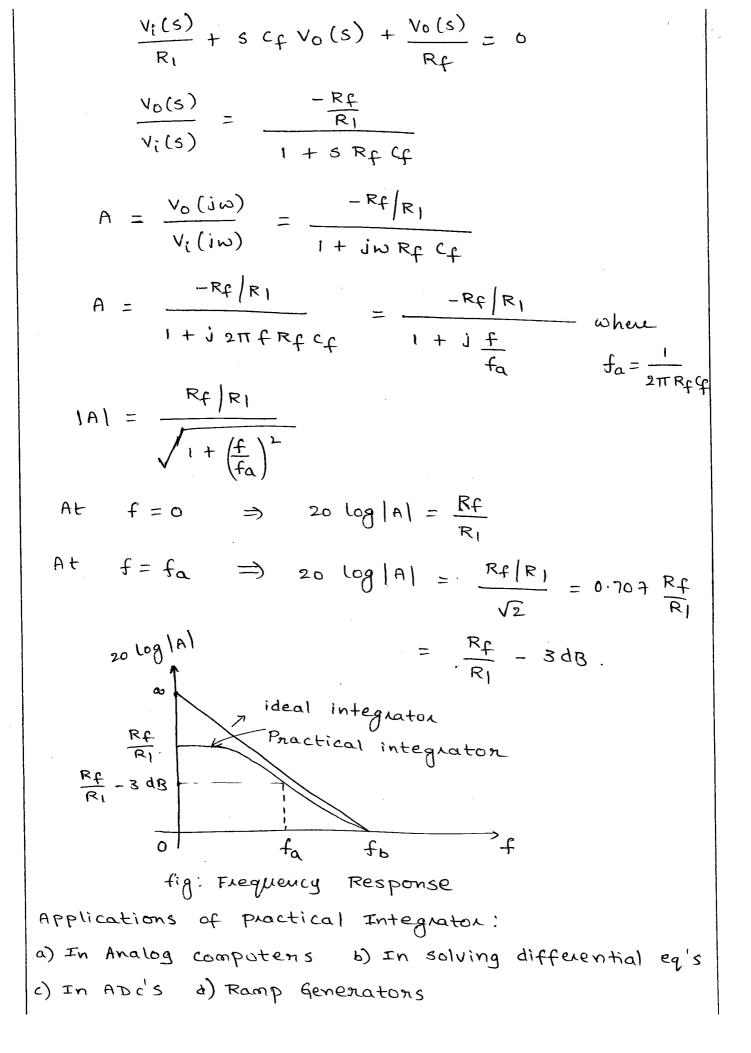

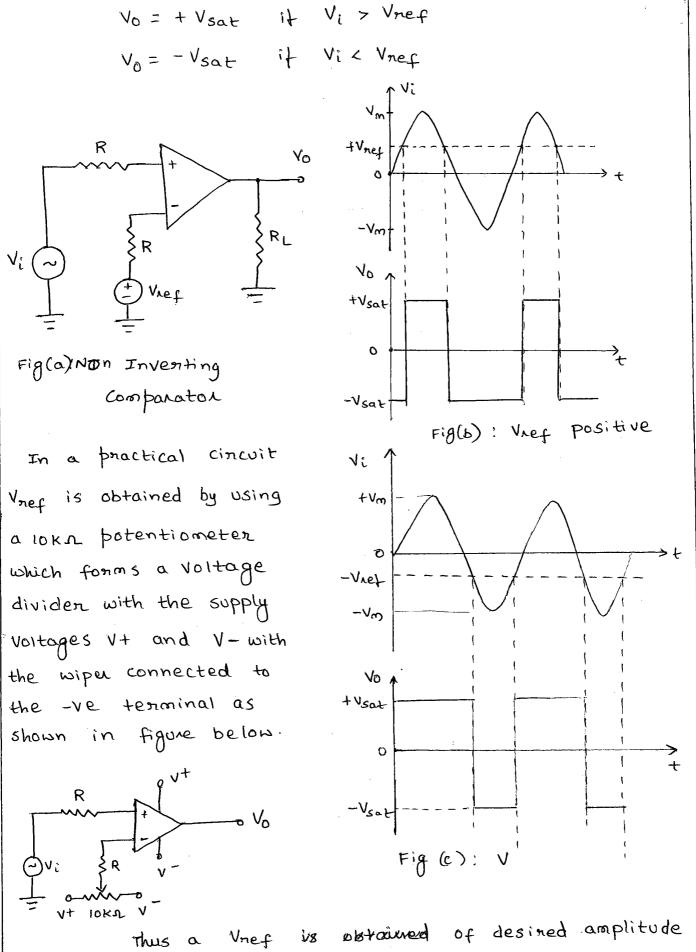

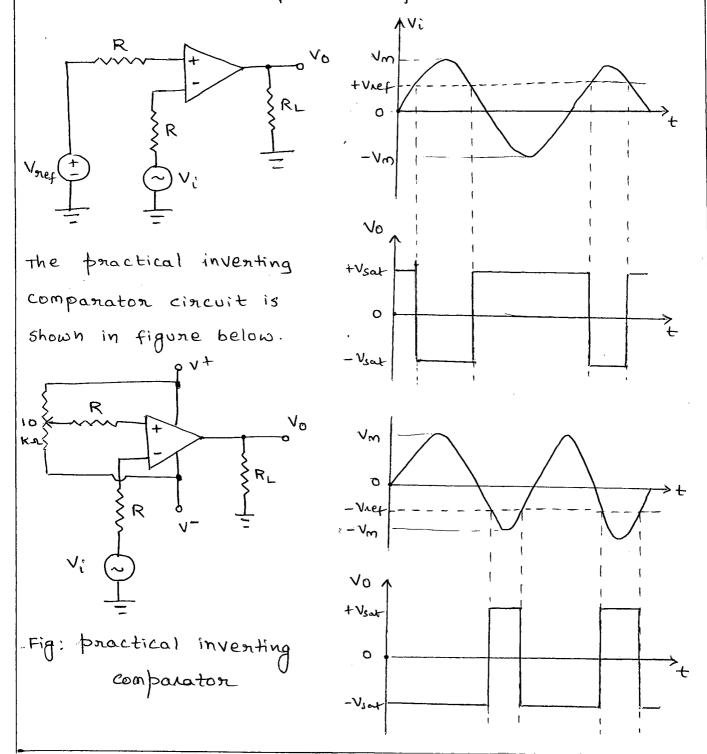

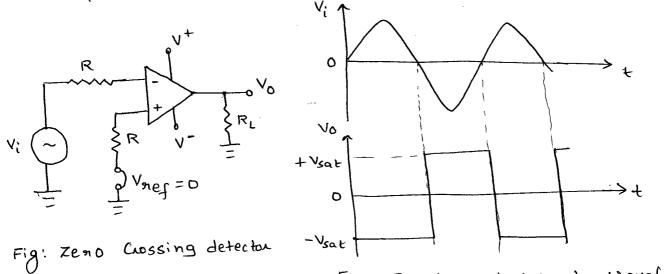

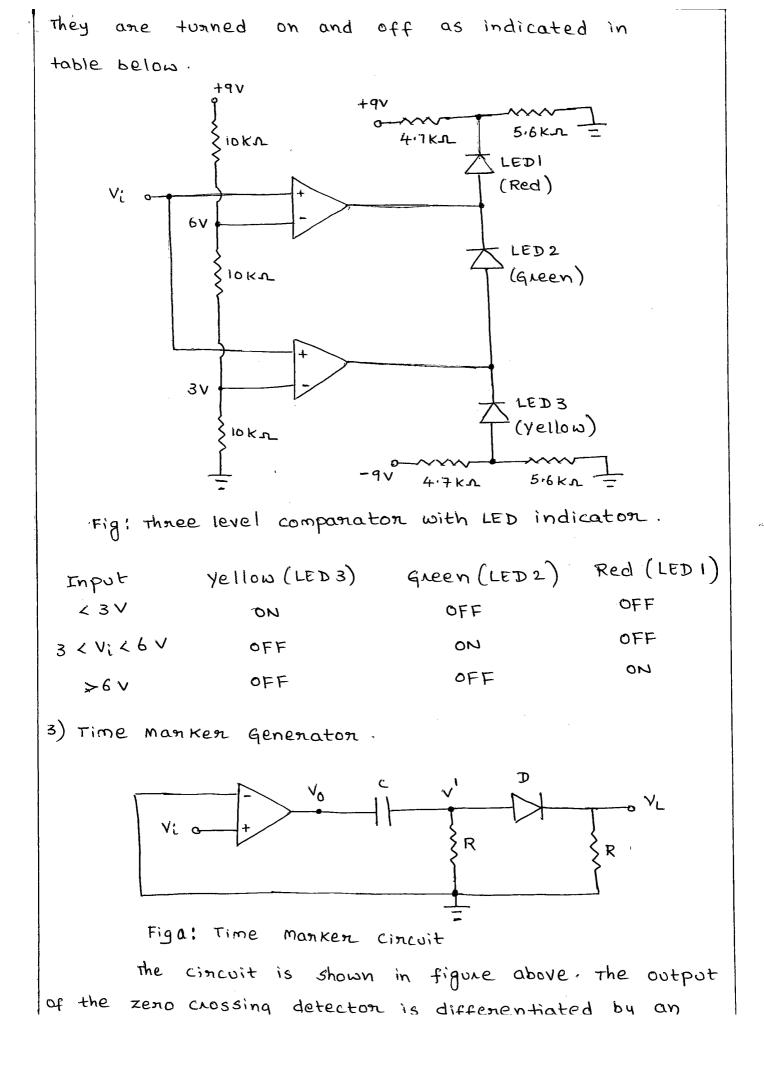

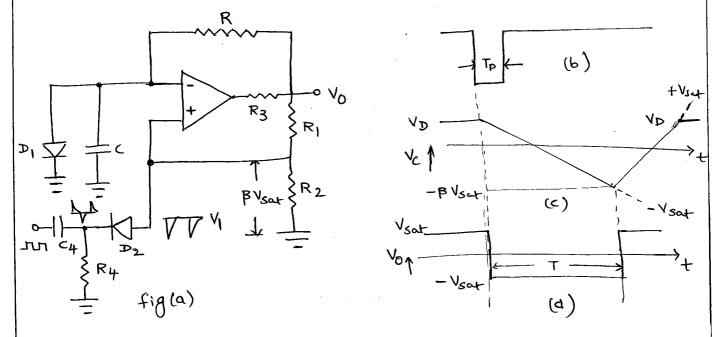

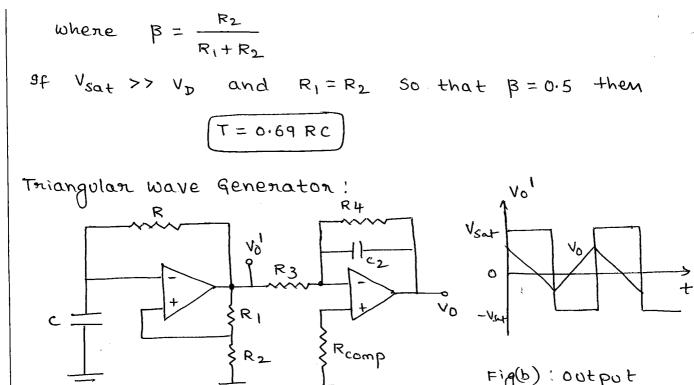

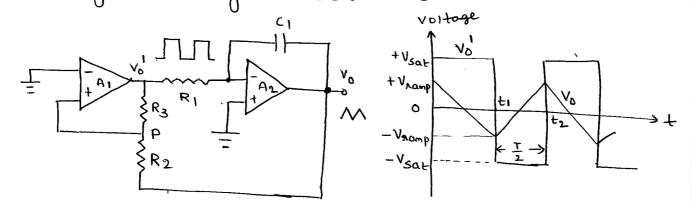

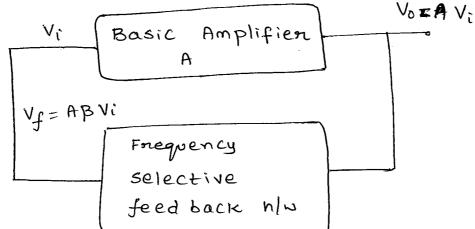

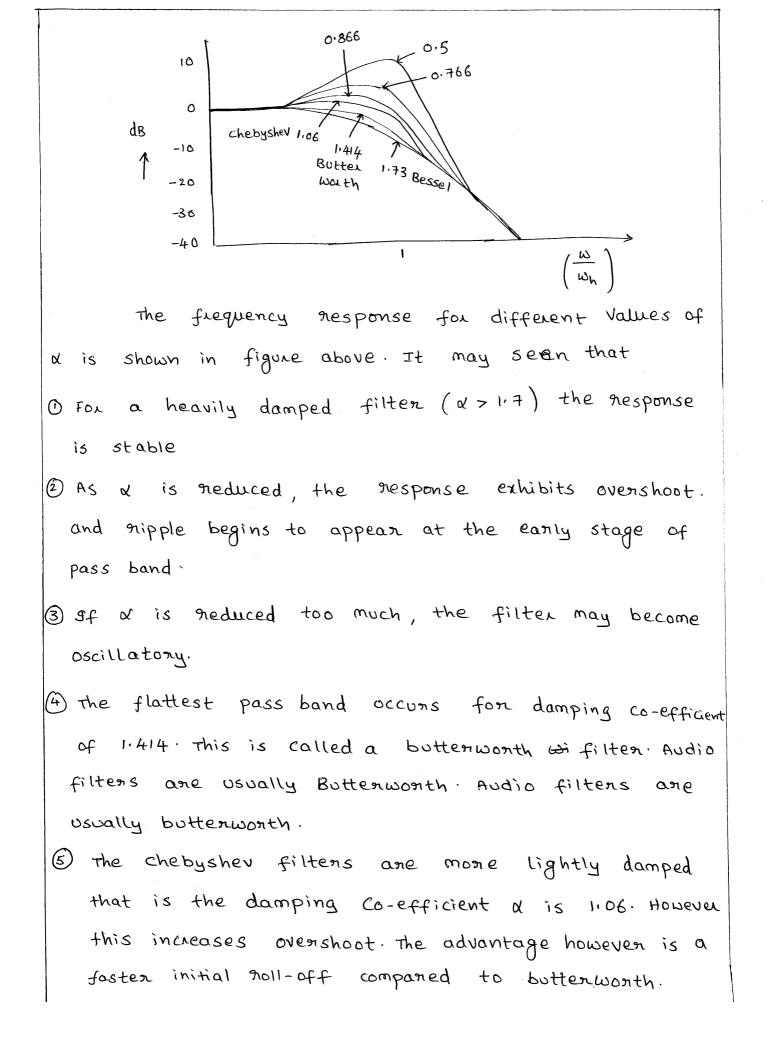

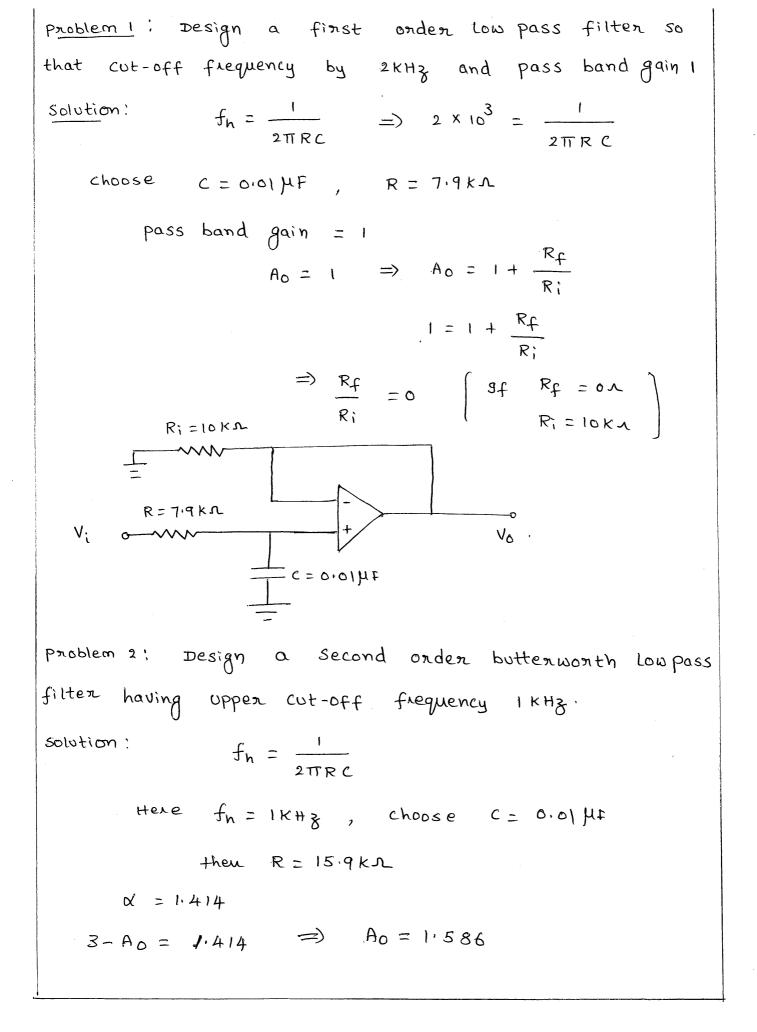

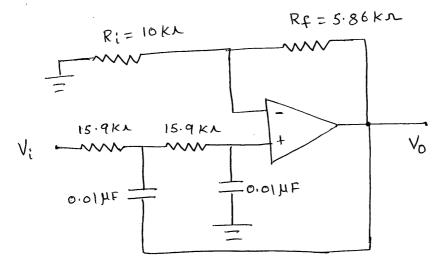

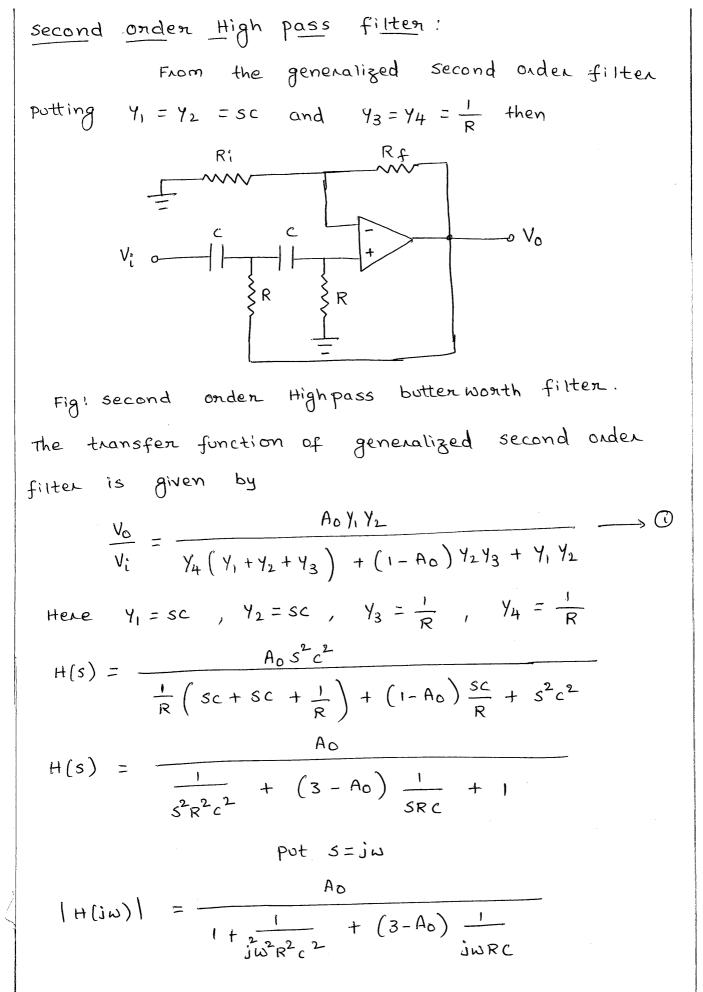

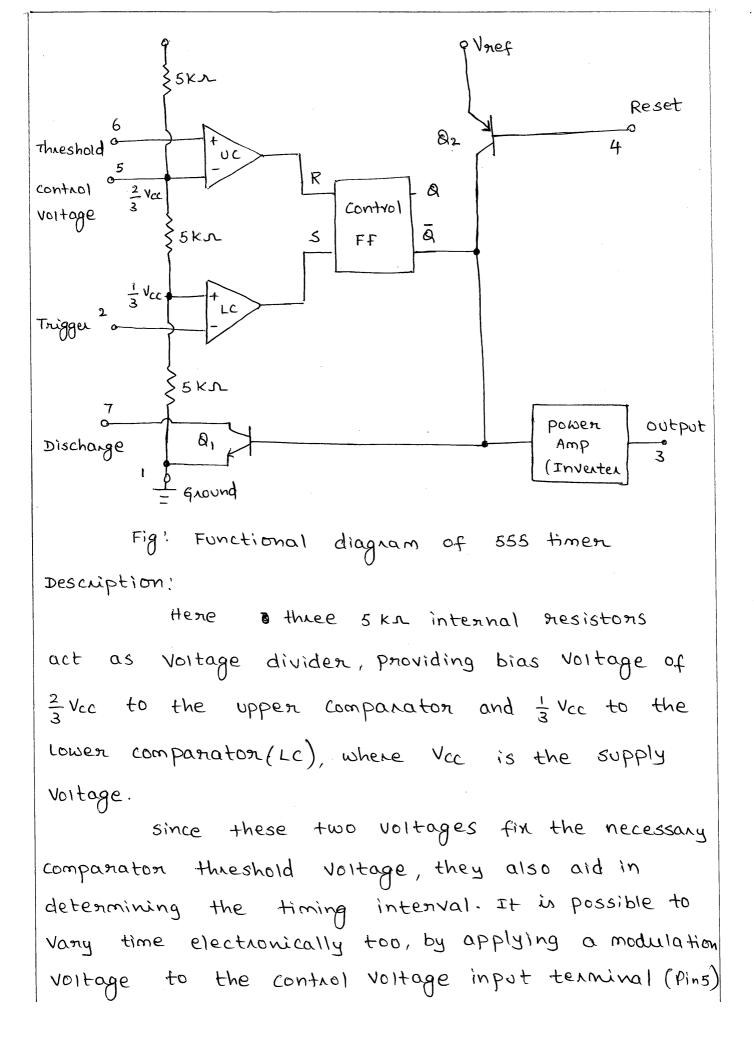

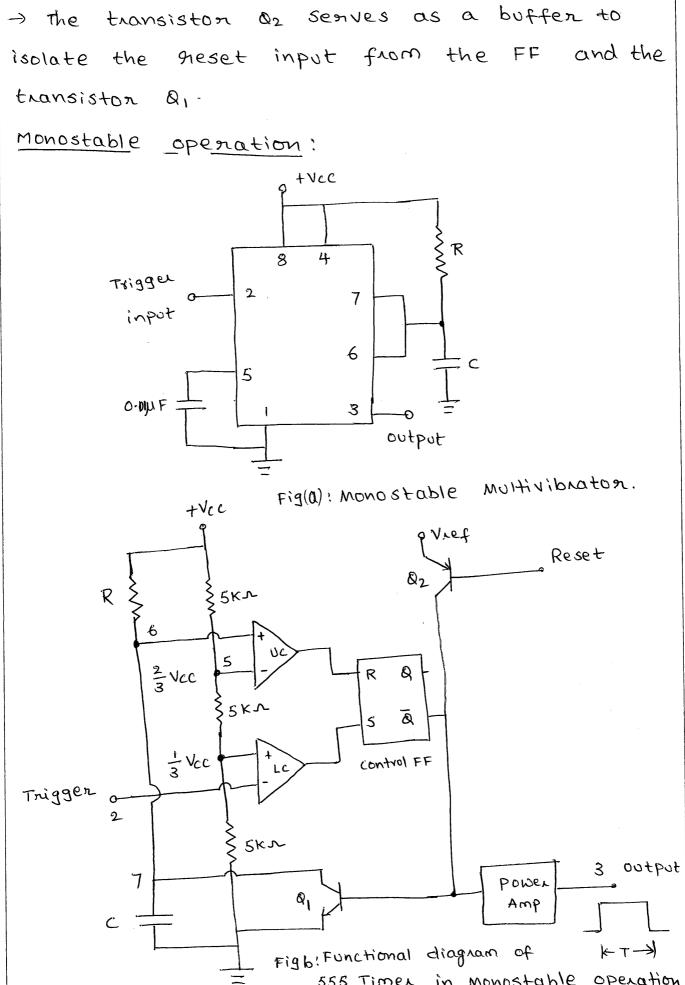

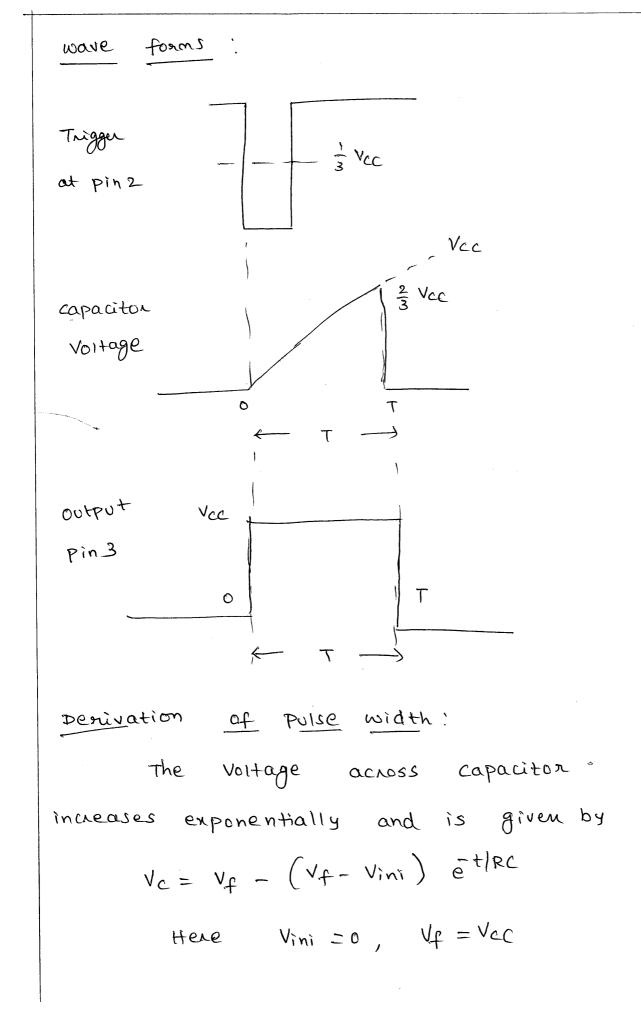

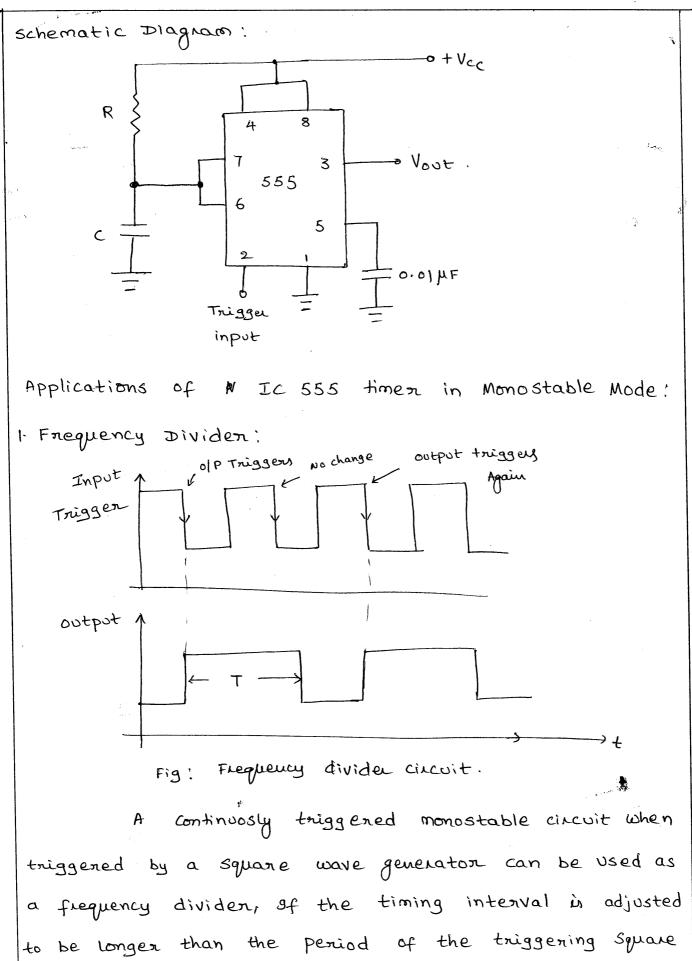

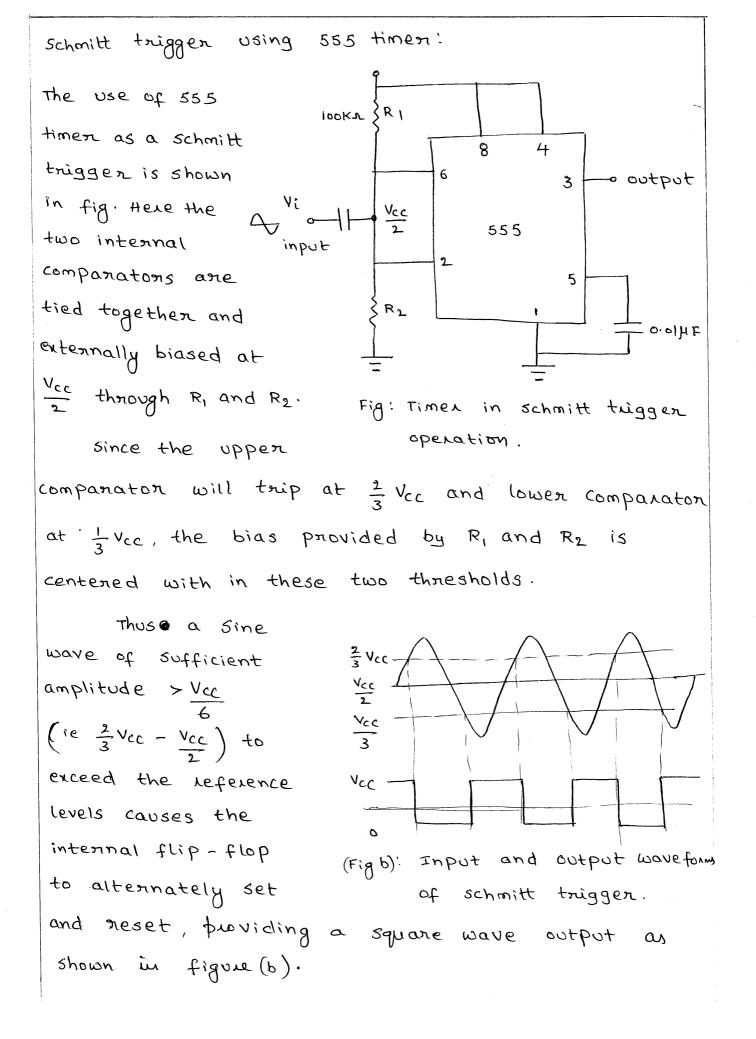

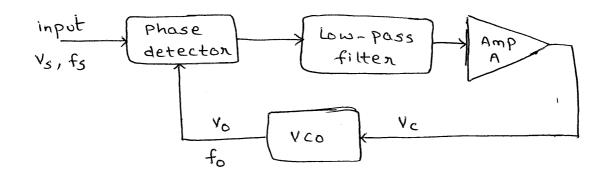

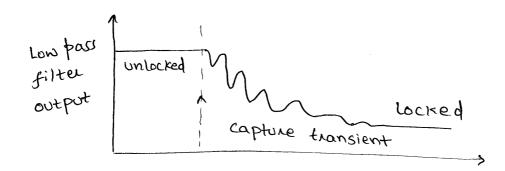

$$\frac{V_0}{V_c} = -\frac{R_f}{R_1 + \frac{1}{S_c}} = -\frac{R_f}{R_1} \left( \frac{1}{1 + \frac{1}{S_{R_1}c}} \right)$$